La conception de produits embarqués à base de mémoire DDR est devenue une routine chez AESTECHNO. Aujourd’hui, développer des produits performants avec de la mémoire vive rapide est indispensable : affichage vidéo fluide, interfaces réactives, traitement de données en temps réel. Nous prenons tous pour acquis la fluidité de nos smartphones et tablettes, mais derrière cette apparente simplicité se cachent des contraintes de conception exigeantes.

Un produit dont la mémoire est mal routée ou mal dimensionnée donne immédiatement un sentiment de lenteur qui nuit à l’image de marque. Il est donc essentiel de maîtriser les fondamentaux du routage DDR pour livrer des produits fiables et performants. Dans cet article, nous partageons notre expérience sur les aspects critiques de la conception LPDDR4 : architecture des signaux, stack-up PCB, impédance contrôlée, gestion du skew, et les pièges courants à éviter.

Qu’est-ce que la LPDDR4 ?

La LPDDR4 est la quatrième génération de mémoire DDR-RAM (Double Data Rate Random Access Memory) en version basse consommation (Low Power). Elle communique les données à deux fois la vitesse de l’horloge, tout en réduisant la tension d’alimentation par rapport à la DDR4 standard, ce qui en fait le choix privilégié pour les systèmes embarqués et mobiles.

Le routage de la LPDDR4 peut sembler mystérieux et complexe, mais il n’en est rien. La LPDDR4 est une variante de la DDR4, elle-même la 4e version de la DDR-RAM. La différence fondamentale avec la DDR4 standard réside dans la topologie : la LPDDR4 utilise une connexion point-à-point entre le SoC et la puce mémoire, tandis que la DDR4 peut fonctionner en bus avec un ou deux DIMM par canal.

La variante Low Power réduit la tension d’alimentation (1,1 V au lieu de 1,2 V pour la DDR4, avec un VDDQ de 0,6 V seulement). En pratique, selon les configurations, la différence de consommation peut varier significativement. C’est le choix naturel pour les SoC ARM comme le NVIDIA Jetson ou le NXP i.MX8, qui intègrent nativement un contrôleur LPDDR4.

Router de la mémoire DDR, ce n’est pas simplement relier des fils. C’est comprendre les phénomènes physiques associés : le signal ne se déplace pas à la vitesse de la lumière, mais à un facteur de celle-ci, déterminé principalement par la constante diélectrique du matériau PCB. Cette vitesse de propagation impacte directement le skew entre signaux. Il faut également maîtriser les concepts d’impédance globale et locale, car tout changement d’impédance génère des réflexions parasites.

Architecture des signaux DDR : groupes DQ, DQS et Command/Address

L’architecture des signaux DDR repose sur une organisation en groupes fonctionnels distincts. Chaque groupe possède ses propres contraintes de routage en termes de longueur, d’impédance et de timing. Comprendre cette structure est la première étape indispensable pour un routage réussi de toute interface mémoire LPDDR4 ou DDR4.

Groupes de données DQ et strobes DQS

La DDR est routée en groupes. Pour une mémoire en configuration x4, nous avons 4 signaux DQ à router avec leur paire différentielle DQS. En configuration x8, ce sont 8 signaux DQ[0-7] avec leur paire DQS. Et en x16, 16 signaux DQ avec deux paires DQS. Dans la pratique, les configurations x4 ou x8 sont plus simples à router. Le routage en x16 est plus complexe car il impose davantage de contraintes d’espacement et de longueur sur une zone réduite du PCB.

Les groupes sont donc des ensembles de DQ. Par exemple, pour une mémoire 32 bits, nous avons 4 groupes de 8 DQ (groupes 0 à 3). Chaque groupe constitue une byte lane : 8 bits de données + 1 paire de strobe DQS + un masque DM. Il est préférable de router toutes les pistes d’un même groupe sur la même couche du PCB, pour des raisons de skew et de reproductibilité industrielle.

Rôle des strobes DQS

Les DQS sont des signaux de strobe différentiels qui servent de référence temporelle locale pour chaque groupe. Leur rôle fondamental est de permettre une longueur légèrement différente entre les groupes. Au lieu de devoir égaliser tous les signaux DDR à la même longueur (ce qui serait extrêmement complexe vu leur nombre), il suffit d’égaliser les signaux au sein de chaque groupe par rapport à leur strobe DQS. Cette architecture par groupes simplifie considérablement le routage.

Groupes Command & Address

Les autres groupes sont les groupes de Command & Address (CA). Ils diffèrent en fonction des technologies (LPDDR vs DDR) et de la topologie interne de la mémoire vive. Point important : ces groupes fonctionnent à la moitié de la vitesse des groupes DQ, ce qui rend leur routage un peu moins critique, bien que les contraintes de skew restent présentes.

Il est essentiel de créer ces groupes dans votre outil de conception PCB dès le début du routage. Un bon groupement permet de résoudre méthodiquement les problèmes de skew et de garantir la conformité aux design rules du fabricant de mémoire. Les problématiques de routage par groupes sont similaires à celles que nous rencontrons sur les interfaces PCI Express, où l’égalisation des longueurs de paires différentielles est tout aussi critique.

Stack-up PCB et choix des matériaux

Le stack-up PCB définit l’empilement des couches conductrices et isolantes qui composent le circuit imprimé. Pour une interface LPDDR4, le choix du stack-up influence directement l’impédance contrôlée, la diaphonie entre signaux et la qualité de l’intégrité du signal. C’est un paramètre de conception qui ne doit jamais être laissé par défaut.

La construction du PCB et de son stack-up démarre au moment où nous commençons le schéma, et se termine vraiment lorsque le routage est finalisé. C’est un processus itératif qui converge vers une solution optimale : le compromis entre performances électriques et coût de fabrication. Si choisir un stack-up par défaut peut suffire pour la majorité des produits, sur un produit avec de la DDR4 ou de la LPDDR4, ce n’est pas une option.

Le Master Drawing

La construction d’un PCB se formalise via l’édition d’un Master Drawing. Ce document rassemble toutes les informations de construction : épaisseurs des couches, matériaux utilisés, finitions de surface, contraintes d’impédance. Industrialiser un PCB, c’est s’assurer de sa fabricabilité dans un environnement industriel, réduire le taux de rebut tout en maintenant les performances au plus près de l’objectif. C’est un compromis entre sous-qualité et sur-qualité.

FR-4 vs matériaux premium

Le FR-4 standard convient à de nombreuses applications, mais pour le routage DDR haute vitesse, ses limites apparaissent rapidement : constante diélectrique peu homogène, pertes élevées à haute fréquence, variations entre lots. Les matériaux premium (Rogers, Isola) offrent des propriétés diélectriques plus stables et prévisibles, mais à un coût significativement supérieur. Nous revenons sur ce compromis coût/performance dans la section simulation.

La question des stubs

Les stubs (bouts de piste non terminés) sont encore tolérés en DDR4 et LPDDR4, à condition de les maîtriser. En revanche, en DDR5 et LPDDR5, les débits sont tels que les stubs deviennent rédhibitoires et doivent être éliminés (back-drilling, via-in-pad). Nous recommandons de commencer à s’en préoccuper dès maintenant, même en LPDDR4, pour préparer la transition vers les générations suivantes. Pour approfondir les techniques de routage haute vitesse, consultez notre guide dédié.

Impédance contrôlée et gestion des réflexions

L’impédance contrôlée garantit que le signal se propage sans perte excessive ni réflexion parasite le long de la piste PCB. En routage LPDDR4, maintenir une impédance constante sur tout le trajet du signal est crucial pour respecter les marges de timing et obtenir des eye diagrams conformes aux spécifications du fabricant.

L’analogie de l’écho dans un tunnel

Pour comprendre l’impédance, imaginons un tunnel. Quand vous criez dans un tunnel, l’écho vous revient. Si votre objectif est de maximiser le son qui arrive au récepteur à l’autre bout, toute cette énergie réfléchie est perdue. Pire : si le signal réfléchi est trop fort, il peut perturber l’émetteur. C’est exactement ce qui se passe sur une piste PCB : chaque discontinuité d’impédance génère une réflexion qui dégrade l’intégrité du signal.

Impédance globale vs impédance locale

L’impédance est une conséquence de la construction géométrique et du choix des matériaux. Le matériau étant identique sur toute la longueur d’une piste, notre travail est fondamentalement un exercice de géométrie. La largeur nominale de la piste est calculée par l’outil de CAO, ce qui ne pose aucun problème pour un bon logiciel. Il faut toutefois bien comprendre l’algorithme de calcul et ses limites.

L’impédance locale, c’est ce qui se passe quand une piste à impédance contrôlée se retrouve à proximité d’un élément non pris en compte dans le calcul nominal : une autre piste, un connecteur, un via, un plan de référence. Un via de masse à proximité d’une piste va influer significativement sur l’impédance locale et générer des réflexions. C’est pourquoi un routage visuellement propre peut être électriquement médiocre si l’environnement immédiat des pistes n’a pas été pris en compte.

Le paramètre S11 : critère de qualité n°1

Nous recommandons de viser un paramètre S11 inferieur ou égal à -15 dB aux fréquences de fonctionnement. Le S11 est le coefficient de réflexion de votre piste : c’est le critère numero 1 pour évaluer la qualité du routage en impédance constante. Un S11 de -15 dB signifie que seulement 3,2 % de la puissance est réfléchie. Au-dessus de -10 dB, les problèmes d’intégrité du signal deviennent significatifs.

Le S11 peut être obtenu par extraction parasitique via un outil de simulation électromagnétique, ou par mesure directe avec un analyseur de réseau vectoriel (VNA). La maîtrise de la compatibilité électromagnétique est étroitement liée à ces problématiques de réflexion et d’intégrité du signal.

Gestion du skew et égalisation des longueurs

Le skew désigne la différence de temps d’arrivée entre deux signaux qui devraient être synchrones. En routage DDR, le skew intra-groupe doit être minimisé pour respecter les fenêtres de setup et hold de la mémoire. Une mauvaise gestion du skew est la cause la plus fréquente de dysfonctionnement intermittent sur les interfaces mémoire haute vitesse.

Setup time et hold time

Un signal qui arrive en retard ou en avance ne va pas respecter les délais acceptables pour la mémoire. Le temps de setup (temps avant le front d’horloge) et le temps de hold (temps après le front d’horloge) définissent la fenêtre dans laquelle les données doivent être stables. La DDR étant un bus parallèle, tous les signaux d’un même groupe doivent arriver au boîtier de RAM au même moment. Les valeurs sont généralement données par les fabricants dans les datasheets, mais nous recommandons de les recalculer systématiquement pour chaque projet.

Contraintes d’égalisation intra-groupe

Au sein d’un même groupe (byte lane), les longueurs de piste doivent être égalisées avec une tolérance typique de +/-25 mils. Les DQS, en tant que strobes locaux, permettent une longueur différente entre les groupes. C’est l’architecture même qui rend le routage faisable : sans cette souplesse inter-groupes, il serait extrêmement difficile d’égaliser des dizaines de signaux.

Impact de la constante diélectrique

La vitesse de propagation du signal dépend directement de la constante diélectrique du matériau PCB. Une variation de cette constante (entre couches, entre zones du PCB, ou entre lots de fabrication) introduit du skew même si les longueurs physiques des pistes sont parfaitement égalisées. C’est pourquoi la longueur maximale acceptable dépend davantage du matériau PCB et de sa construction que des recommandations brutes du fabricant de mémoire. Être légèrement plus long n’est pas dramatique avec un bon matériau et un routage soigné.

Conseil pratique : placement de la mémoire

Chez AESTECHNO, nous avons constaté qu’il est souvent préférable de placer la mémoire un peu plus éloignée du SoC quand on débute en routage DDR. Cela peut sembler contre-intuitif, mais un espacement suffisant donne plus de marge pour ajuster les longueurs des pistes et respecter les contraintes de skew. En revanche, sur un design très contraint en surface, un placement proche nécessite une maîtrise avancée du routage, similaire aux défis rencontrés en conception de systèmes embarqués compacts.

LPDDR4 vs DDR4 vs DDR5 : comparatif technique

Le choix entre les différentes technologies de mémoire DDR dépend du contexte applicatif : consommation, bande passante, topologie, complexité de routage. Ce tableau comparatif synthétise les caractéristiques principales pour aider à la décision technique lors de la phase de rédaction du cahier des charges.

| Caractéristique | LPDDR4/4x | DDR4 | DDR5 | LPDDR5 |

|---|---|---|---|---|

| Débit max par broche (MT/s) | 4266 | 3200 | 6400 | 6400 |

| Tension (V) | 1,1 / 0,6 (VDDQ) | 1,2 | 1,1 | 0,5 (VDDQ) |

| Topologie | Point-à-point | Bus (1-2 DIMM/canal) | Point-à-point | Point-à-point |

| Largeur canal | 16 bits (x2 canaux) | 64 bits | 32 bits (x2 sub-ch) | 16 bits (x2 canaux) |

| Stubs | Tolérés (attention) | Tolérés | Proscrits | Proscrits |

| Cas d’usage | Embarqué, mobile, SoC ARM | Serveurs, PC, industriel fixe | Serveurs, PC haut de gamme, IA | Mobile next-gen, embarqué IA |

Pour un comparatif détaillé entre DDR4 et DDR5, consultez notre guide DDR4 vs DDR5 qui détaille les évolutions entre ces deux générations et leurs implications concrètes sur la conception.

Simulation et validation

La simulation électromagnétique et la validation par mesure sont les deux piliers de la vérification d’une interface mémoire DDR. Elles permettent de confirmer que l’impédance, le skew et les marges de timing respectent les spécifications avant de lancer la fabrication, évitant ainsi des itérations coûteuses de prototypage.

Outils de simulation EM

Les outils de simulation électromagnétique (HFSS, CST, HyperLynx) permettent d’extraire les paramètres S, de vérifier l’impédance locale, et de simuler les eye diagrams avant fabrication. Ces outils sont complexes et nécessitent une expertise pointue. Si vous ne maîtrisez pas ces outils, nous recommandons de faire appel à un spécialiste plutôt que de risquer des résultats mal interprétés.

Notre flux ANSYS SIwave pour la simulation DDR

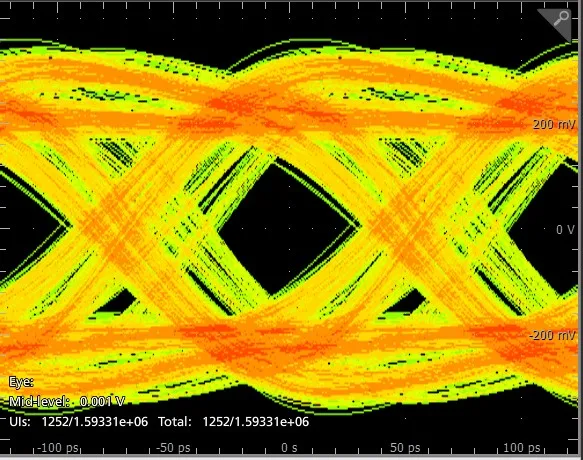

Chez AESTECHNO, nous simulons systématiquement les bus LPDDR4 avec ANSYS SIwave pour l’intégrité du signal (SI) et l’intégrité de l’alimentation (PI). Nous extrayons les paramètres S des byte-lanes DQ/DQS, nous vérifions le length-matching intra-groupe, nous simulons le eye diagram à 4266 Mbps et nous analysons le PDN jusqu’à plusieurs centaines de MHz. Résultat concret : nous pouvons dire avant fabrication si le bus va fonctionner, avec une bonne précision. Cette capacité — rare dans le marché français des bureaux d’études, car les licences ANSYS représentent un investissement significatif — sécurise le premier prototype et évite les re-spin coûteux.

Sélection du matériau PCB pour LPDDR4

Nous sommes experts dans le choix du matériau PCB adapté à chaque projet DDR. Pour le LPDDR4 à 4266 Mbps, nous privilégions souvent Isola IS410 ou 370HR : Dk stable, faible dispersion de Df entre couches, et Tg élevé compatible avec plusieurs cycles Pb-free. Pour les designs DDR5 ou PCIe Gen5 combinés, nous montons en Megtron 6/7. Nous arbitrons Dk, Df, Tg, CTE, stabilité thermique, disponibilité fabricant et coût pour chaque cahier des charges, y compris sur des stackups jusqu’à 28 couches avec µVias laser et vias enterrés.

Eye diagrams et validation S11

L’eye diagram est la représentation graphique qui synthétise la qualité globale d’un lien mémoire : il intègre l’effet du skew, des réflexions, de la diaphonie et de l’atténuation. Un eye diagram ouvert signifie que les marges de timing et de tension sont suffisantes. Le S11 mesuré au VNA complète cette analyse en identifiant précisément les fréquences auxquelles des réflexions apparaissent. Pour en savoir plus sur les méthodologies de test et validation, consultez notre guide dédié.

Le compromis simulation vs matériaux

Utiliser un matériau bon marché a un coût caché : il faut compenser par davantage de simulations pour valider le design. Les matériaux premium (Rogers, Isola) offrent des propriétés diélectriques plus stables et tolèrent mieux les imperfections de routage, mais à un coût de fabrication supérieur. Nous constatons que l’investissement en simulation permet souvent de réduire le coût des matériaux en optimisant le design pour fonctionner correctement sur du FR-4 standard. C’est un arbitrage à faire au cas par cas, en fonction des volumes de production et des contraintes de performance.

Pièges courants et retours d’expérience

Le routage DDR est un domaine où l’expérience pratique fait toute la différence entre un prototype qui fonctionne et un produit certifiable en production. Chez AESTECHNO, nous avons identifié plusieurs erreurs récurrentes qui coûtent cher en itérations de conception et en retards de mise sur le marché.

Notre expertise DDR : un portfolio multi-générations

Chez AESTECHNO, notre portfolio mémoire couvre les quatre générations déployées en production : DDR2, DDR3, DDR4 et LPDDR4. Cette continuité est précieuse : les pièges qui apparaissaient en DDR3 se retrouvent amplifiés en LPDDR4, et la compréhension fine de chaque génération permet d’anticiper les contraintes de la suivante. Nous avons également audité de nombreux bus mémoire clients à l’aide de mesures par diagrammes de l’oeil, révélant régulièrement des défauts d’intégrité de signal invisibles en fonctionnement nominal mais critiques en production série.

Au Q1 2026, nous avons livré un projet particulièrement exigeant autour du Jetson Orin NX de NVIDIA, avec interface LPDDR4x native et BSP Yocto entièrement customisé. Ce type de projet concentre toutes les difficultés du routage LPDDR4 moderne : contraintes de timing serrées, topologie point-à-point contrainte par le package du SoC, et validation par eye diagrams sur le prototype. Une expérience directe qui nourrit chacune des recommandations de cet article.

Les exemples en ligne : prudence

Chez AESTECHNO, nous avons constaté que la majorité des exemples de routage DDR disponibles sur Internet sont techniquement défaillants. Nous vous conseillons fortement de rester critique. Bon nombre de ces articles proposent des exemples visuellement séduisants, mais quand on acquiert une expérience plus poussée, on se rend vite compte que le routage, bien que joli, est au final assez mauvais. La plupart du temps, ces routages ne respectent pas les groupes. Oublier cela, c’est concevoir un produit uniquement bon pour le prototype. En production, ce type de routage ne tient pas longtemps face aux variations de process, de température et au vieillissement des composants.

Les normes IPC : base essentielle mais insuffisante

Nous rappelons que les normes IPC ne sont pas obligatoires. Elles sont là pour simplifier la communication et se mettre d’accord sur des standards industriels. Dans certains cas, l’industrie est en avance sur les normes IPC. Il faut en être conscient : appliquer 100 % IPC n’est pas toujours possible ni souhaitable. Parfois l’IPC ne définit pas de solution pour un cas spécifique. La définition même du métier d’ingénieur est de savoir faire des compromis éclairés. En routage DDR, connaître les IPC est essentiel. Mais souvent, comme dans tout routage complexe, il est nécessaire de s’en affranchir avec justification technique.

Erreurs récurrentes à éviter

- Groupes non respectés : le design fonctionne en prototype (conditions idéales) mais échoue en production (variations ±40 °C, composants worst-case, vieillissement). C’est la différence entre « ça marche » et « certifiable ».

- Stack-up par défaut : utiliser le stack-up standard du fabricant de PCB sans l’adapter aux contraintes DDR est une source fréquente de problèmes d’impédance.

- Matériaux inadaptés : choisir un matériau bas de gamme sans compenser par de la simulation revient à jouer avec le feu sur un produit série.

- Références de plan discontinues : une piste qui change de plan de référence sans via de couture subit une rupture d’impédance locale difficile à détecter sans simulation.

LPDDR4 : un choix stratégique pour vos produits embarqués

Le choix de la technologie mémoire est une décision stratégique qui impacte directement la compétitivité de vos produits. Chez AESTECHNO, nous accompagnons régulièrement des directeurs techniques et des décideurs dans cette réflexion, car la mémoire influence trois axes fondamentaux : la performance perçue par l’utilisateur, l’autonomie sur batterie et le comportement thermique du produit.

Performance et expérience utilisateur

La LPDDR4 offre une bande passante suffisante pour la majorité des applications embarquées actuelles : affichage vidéo fluide, traitement d’images, interfaces utilisateur réactives. Pour un produit destiné au marché grand public ou industriel, une mémoire sous-dimensionnée se traduit immédiatement par une perception de lenteur qui nuit à l’image de marque.

Autonomie et contraintes thermiques

La variante Low Power de la DDR4 réduit la consommation par rapport à la DDR4 standard. Dans un produit sur batterie — smartphone, tablette industrielle, terminal portable — ce gain est un avantage concurrentiel direct. De plus, une consommation réduite signifie moins de dissipation thermique, ce qui simplifie la conception mécanique et réduit les risques de throttling en environnement contraint.

LPDDR4, DDR4 ou DDR5 : quel choix pour votre projet ?

Nous avons constaté que le choix entre ces technologies dépend principalement du contexte produit :

- LPDDR4/LPDDR4x : produits sur batterie, embarqué compact, contraintes thermiques fortes. C’est le choix naturel pour les SoC ARM (type NVIDIA Jetson, NXP i.MX8).

- DDR4 : applications industrielles fixes, systèmes sans contrainte d’autonomie, budgets serrés. Excellente maturité industrielle et chaîne d’approvisionnement stable.

- DDR5 : projets nécessitant une bande passante élevée (IA, traitement vidéo multi-flux) ou une durée de vie produit longue. Consultez notre guide DDR4 vs DDR5 pour approfondir cette comparaison.

Impact sur la longévité produit

La LPDDR4 bénéficie aujourd’hui d’une maturité industrielle solide, avec de nombreux fabricants et une disponibilité stable. Pour un produit dont la durée de vie dépasse 5 à 7 ans, nous recommandons de vérifier les roadmaps de fin de vie des composants mémoire dès la phase de conception. Un choix mémoire mal anticipé peut entraîner un redesign coûteux en milieu de cycle de vie.

Projet avec LPDDR4/DDR5 ? Expertise AESTECHNO

Le routage mémoire haute vitesse est notre spécialité. Nos experts vous accompagnent :

- Stack-up PCB optimisé pour DDR/LPDDR

- Simulation intégrité signal et eye diagrams

- Routage groupes DQ/DQS conforme aux design rules

- Validation S11 et qualification industrielle

Pourquoi Choisir AESTECHNO ?

- 10+ ans d’expertise en routage DDR/LPDDR haute vitesse

- 100% de réussite aux certifications CE/FCC

- Bureau d’études français basé à Montpellier

Article rédigé par Hugues Orgitello, ingénieur en conception électronique et fondateur d’AESTECHNO. Profil LinkedIn.

Articles Connexes

- Design High-Speed et Intégrité du Signal — Méthodologie pour routages critiques

- DDR4 vs DDR5 — Évolutions et contraintes de conception

- Processeurs Jetson NVIDIA — LPDDR4x pour IA embarquée

- Conception de PCB — Stack-up et matériaux

- Conception Produits Électroniques — Méthodologie de conception

FAQ : LPDDR4 et Routage Mémoire

Qu’est-ce que le paramètre S11 et pourquoi viser -15 dB ?

Le S11 mesure le taux de réflexion du signal sur une piste (coefficient de réflexion). Un S11 de -15 dB signifie que très peu d’énergie est réfléchie et que la quasi-totalité est transmise, ce qui est excellent pour l’intégrité du signal. Un S11 supérieur à -10 dB indique des problèmes d’impédance avec des réflexions importantes. Le S11 s’obtient par simulation électromagnétique (extraction parasitique) ou mesure avec un analyseur de réseau vectoriel (VNA). Pour LPDDR4/DDR4, un bon S11 garantit des eye diagrams conformes.

Pourquoi les simulations électromagnétiques sont-elles si coûteuses pour les interfaces DDR ?

Les outils de simulation EM (HFSS, CST, HyperLynx) nécessitent des licences coûteuses, une expertise technique pointue avec une formation longue, et un temps de calcul important pour les modèles 3D complexes. Cependant, elles permettent d’utiliser des matériaux PCB économiques en compensant par un design optimisé. L’alternative est d’utiliser des matériaux premium (Rogers, Isola) qui tolèrent mieux les imperfections mais coûtent significativement plus cher que le FR-4 standard.

Que signifie « respecter les groupes » en routage DDR ?

En DDR, les signaux sont organisés en groupes (byte lanes) : 8 bits de données DQ + 1 paire de strobe DQS + masque DM. Tous les signaux d’un même groupe doivent avoir des longueurs égalisées (±25 mils) et arriver simultanément pour respecter les fenêtres de setup/hold. Ne pas respecter les groupes fonctionne en prototype (contraintes timing relâchées) mais échoue en production industrielle (variations process, températures, vieillissement). C’est la différence entre « ça marche » et « certifiable ».

Les normes IPC sont-elles suffisantes pour le routage DDR complexe ?

Les normes IPC fournissent une base essentielle (largeurs de pistes, espacements, empilements standards) mais ne couvrent pas tous les cas avancés : routages DDR très haute vitesse (>3200 MT/s), contraintes spécifiques des fabricants (variations process), optimisations pour matériaux non-standard. Sur des projets complexes, il faut parfois déroger aux IPC avec justification technique (simulations, mesures). Le métier d’ingénieur consiste à faire des compromis éclairés entre normes, coûts et performance.

Pourquoi tant d’exemples de routage DDR sur Internet sont-ils mauvais ?

Beaucoup de tutoriels montrent des routages visuellement corrects mais techniquement défaillants : groupes non respectés, longueurs mal égalisées, références de plan discontinues, stubs excessifs. Ces routages peuvent fonctionner sur des prototypes en conditions idéales (température stable, composants triés) mais échouent en production (variations ±40 °C, composants worst-case, vieillissement). Pour du matériel certifiable industriel, il faut suivre les design guides des fabricants de SoC/mémoire et valider par eye diagrams.