25 min de lecture Hugues Orgitello

Conception PCB high-speed : intégrité signal et stack-up

Conception haute vitesse DDR5, PCIe, USB 3 : stack-up, impédance contrôlée, simulations SI/PI. Méthodologie right-first-time par AESTECHNO, Montpellier.

La conception haute vitesse (high-speed design) concerne les signaux DDR5 (jusqu'à 6400 MT/s, rise time ~75 ps), PCIe Gen 5 (32 GT/s par lane, BER cible 1e-12), USB 3.2 Gen 2x2 (20 Gbps) et HDMI 2.1 (48 Gbps). Bureau d'études basé à Montpellier, nous concevons ces systèmes depuis plus de 10 ans avec une exigence right-first-time : chaque stack-up, chaque impédance, chaque stub est validé avant gravure.

Chez AESTECHNO, nous avons constaté qu'une paire différentielle (differential pair) mal routée compromet l'intégrité de signal bien avant que le masque PCIe de compliance ne se ferme. L'empilement (stackup) et l'impédance (impedance) contrôlée restent les deux leviers les plus rentables à figer tôt.

En résumé

- Stack-up : 6 couches pour DDR4 3200 MT/s, 8-12 couches pour DDR5 6400 MT/s et PCIe Gen 5 32 GT/s.

- Impédance contrôlée : 50 Ω single-ended, 90 Ω USB, 100 Ω différentiel PCIe/Ethernet, ±10 % IPC-2221 classe 2, ±5 % classe 3.

- Matériaux : FR4 jusqu'à 2 GHz, FR4 High-Tg jusqu'à 5 GHz, Megtron 6 (Df 0,004) et Rogers RO4350B (εr 3,48) pour PCIe Gen 4/5.

- Simulations SI/PI ANSYS SIwave + modèles IBIS/AMI obligatoires au-delà de 10 Gbps, validées aux corners.

- Compliance : 10GbE < 6 dB à 2,5 GHz (IEEE 802.3), PCIe Gen 5 < 30 dB à 16 GHz, DDR5 tCK ≈ 312 ps (JEDEC JESD79-5).

Sommaire

- Pourquoi la conception haute vitesse est un enjeu critique.

- Exigences par type de signal : stack-up et simulation.

- Méthodologie de conception haute vitesse en 7 étapes.

- FR4 vs Rogers : comment choisir le matériau PCB ?

- Notre service d'audit de bus numériques.

- Pourquoi choisir AESTECHNO pour vos projets haute vitesse.

- En résumé.

Pourquoi la conception haute vitesse est un enjeu critique

La conception haute vitesse concerne tout signal dont le temps de montée est suffisamment court pour que les effets de ligne de transmission deviennent significatifs. En pratique, dès que la longueur d'une piste PCB (trace) dépasse λ/6 de la longueur d'onde du signal, l'impédance caractéristique (impedance), les réflexions et le couplage entre pistes conditionnent le fonctionnement. La compatibilité électromagnétique (EMC, CEM) devient alors inséparable de l'intégrité de signal : un via mal drainé rayonne comme une antenne parasite. Cette réalité s'impose à la majorité des projets embarqués : même un système IoT peut intégrer de la DDR5 à 4800 MT/s (rise time < 100 ps) ou du PCIe Gen 3 à 8 GT/s. Les cibles d'œil typiques post-equalization sont une ouverture verticale > 150 mV et horizontale > 0,5 UI, sous peine d'échec en compliance.

Les conséquences d'un design high-speed mal maîtrisé sont rarement visibles sur le premier prototype. Les mécanismes de correction d'erreurs (ECC, retransmissions) masquent les défauts. C'est en production, face à la variabilité des composants et des lots de PCB, que les problèmes émergent : taux de rejet élevé, instabilités en température, échecs de certification CEM. Le coût d'une reprise à ce stade peut retarder un lancement de plusieurs mois.

Notre équipe maîtrise l'ensemble de la chaîne de conception haute vitesse. Cette expertise complète nos compétences en conception de cartes RF et certification radio, couvrant ainsi l'intégralité du spectre électromagnétique que rencontrent les systèmes électroniques modernes.

Pré-qualification de conformité interne. Notre laboratoire dispose d'un oscilloscope Tektronix équipé de la suite TekExpress, qui couvre les tests de conformité PCI Express, USB 3.x, MIPI (D-PHY, C-PHY, M-PHY), DDR2 / DDR3 / DDR4, HDMI, Ethernet et LVDS. Cette capacité de mesure interne nous permet de valider les eye diagrams, de régler les égaliseurs (pre-emphasis, de-emphasis, CTLE) et de capturer les marges de timing avant le tape-out de production. Concrètement, le délai entre une révision de routage et sa validation électrique tombe d'un cycle de laboratoire externe (plusieurs semaines) à une journée de mesure en interne.

Exigences par type de signal : stack-up et simulation

Le niveau de complexité d'un projet haute vitesse dépend directement des interfaces utilisées. Le tableau ci-dessous synthétise les exigences typiques que nous appliquons en fonction du type de signal. Ces recommandations sont le fruit de notre expérience sur des projets réels et peuvent varier selon les contraintes spécifiques de chaque application.

| Type de signal | Débit / Fréquence | Stack-up recommandé | Simulation requise |

|---|---|---|---|

| DDR4 | 3200 MT/s | 6 couches minimum | SI pré-layout |

| DDR5 | 4800-6400 MT/s | 8-12 couches | SI + PI pré et post-layout |

| LPDDR4/4X | 4266 MT/s | 8 couches minimum | SI + PI |

| PCIe Gen3 | 8 GT/s | 6 couches minimum | SI pré-layout |

| PCIe Gen4/Gen5 | 16-32 GT/s | 8+ couches, matériaux faible perte | SI + PI post-layout, extraction 3D |

| USB 3.2 Gen2 | 10 Gbps | 6 couches minimum | SI |

| HDMI 2.1 | 12 Gbps par lane | 8+ couches | SI + PI |

Pour approfondir les contraintes spécifiques aux interfaces mémoire, consultez notre comparatif DDR4 vs DDR5 et notre guide sur les secrets de la LPDDR4.

Méthodologie de conception haute vitesse en 7 étapes

La réussite d'un projet high-speed repose sur une méthodologie rigoureuse appliquée dès les premières phases. Nous suivons un processus structuré qui intègre l'intégrité de signal à chaque étape, du cadrage initial jusqu'à la vie série. Cette approche systématique est ce qui garantit le right-first-time sur les projets les plus exigeants.

1. Cadrage technique et fonctionnel

Tout projet haute vitesse commence par une phase d'analyse qui conditionne la suite du développement. L'objectif est d'identifier les signaux critiques, de quantifier les marges disponibles et d'évaluer les risques techniques avant le moindre trait de schéma. Les questions fondamentales à traiter :

- Quels sont les signaux les plus rapides et leur débit cible ?

- Quel est le budget de pertes acceptable sur chaque canal de transmission ?

- Quelles normes de conformité s'appliquent (PCIe compliance, JEDEC pour DDR) ?

- L'équipe dispose-t-elle d'une expérience validée sur ces interfaces ?

Cette phase de cadrage est le moment où nous définissons le niveau de simulation nécessaire et le type de stack-up PCB à viser. Un cadrage rigoureux permet d'éviter les itérations coûteuses en aval. Pour les projets impliquant des cartes FPGA, cette étape inclut l'analyse des transceivers sériels et de leurs contraintes de placement.

2. Architecture électronique et logicielle

L'architecture d'un système haute performance ne se résume pas au choix du processeur. Elle implique une co-conception matérielle et logicielle où chaque décision impacte l'intégrité de signal. Le choix d'un SoC détermine les interfaces mémoire disponibles, les protocoles série supportés et les contraintes de placement des composants critiques. En parallèle, le développement logiciel sur certaines cibles haute performance présente ses propres complexités : configuration des équaliseurs, réglage des terminaisons ODT, tuning des timings mémoire.

Nous travaillons en étroite collaboration entre concepteurs hardware et développeurs firmware pour garantir que les paramètres d'égalisation, de pré-emphasis et de terminaison soient optimisés conjointement.

3. Stack-up PCB et choix des matériaux

Le stack-up est le fondement de tout design haute vitesse. C'est ici que se joue une part déterminante de la réussite du projet, car il conditionne l'impédance caractéristique des pistes, l'isolation entre signaux et la qualité des plans de référence. Un stack-up mal dimensionné ne se rattrape pas en routage.

Pour un projet DDR5 à 4800 MT/s, un stack-up de 8 à 12 couches est typiquement nécessaire, avec des plans de masse continus sous chaque couche de signal. D'après Panasonic, fabricant du Megtron, et selon Rogers Corporation, les matériaux basses pertes comme le Megtron 6 (Df ~0,004), le Tachyon 100G (Df ~0,0021) ou le Rogers RO4350B (εr = 3,48, Df = 0,0037 @ 10 GHz) deviennent indispensables pour les interfaces PCIe Gen 4/Gen 5 et les bus DDR5 à 6400 MT/s, au-delà de 5 GHz, le FR4 standard (εr ≈ 4,4, Df ~0,020) atteint ses limites en termes de pertes diélectriques.

FR4 vs Rogers : comment choisir ? Un FR4 amélioré (Isola IS415, Df ~0,012) couvre la plupart des projets jusqu'à PCIe Gen 3 / 10GbE avec un surcoût matière limité. Au-delà, l'écart devient mesurable : sur un canal de 20 cm à 16 GHz, le FR4 standard accuse une insertion loss > 12 dB alors qu'un Megtron 6 reste sous 6 dB. Le Rogers RO4350B s'impose dès qu'on mixe numérique haute vitesse et RF au-delà de 6 GHz sur la même carte. Règle pragmatique : prendre le matériau le moins cher qui passe le budget de pertes canal, pas « le meilleur disponible ».

Nous définissons chaque stack-up en collaboration directe avec le fabricant PCB, en utilisant des outils de calcul d'impédance comme Polar SI9000 pour garantir les valeurs cibles, 50 Ω single-ended, 90 Ω USB, 100 Ω différentiel Ethernet/PCIe, avec des tolérances de ±10% (classe 2 IPC-2221) ou ±5% (classe 3 pour PCIe Gen 5 et DDR5) reproductibles en production. Les épaisseurs de cuivre standard sont 0,5 oz (18 µm) pour les couches internes de signal et 1 oz (35 µm) pour les plans de puissance. Cette approche s'inscrit dans notre démarche globale de Design for Manufacturing (DFM), indispensable sur les cartes haute performance.

Stripline vs microstrip : à impédance égale, une stripline enfouie entre deux plans de masse offre un crosstalk typiquement 15 à 20 dB inférieur à un microstrip de surface, au prix d'une couche de routage moins accessible. Nous routons systématiquement PCIe Gen 4/Gen 5, DDR5 et USB4 en stripline pour tenir le budget canal défini par IEEE 802.3 (insertion loss < 6 dB à 2,5 GHz Nyquist pour 10GbE), et réservons les microstrips aux signaux non critiques et aux antennes imprimées. Pre-emphasis vs equalization adaptative : le pre-emphasis émetteur compense le canal connu à la conception ; le DFE/CTLE récepteur corrige en temps réel selon le canal réel, au-delà de 16 GT/s (PCIe Gen 4+), les deux sont combinés systématiquement.

4. Routage haute vitesse

Le routage d'un design haute vitesse obéit à des règles strictes dont le non-respect compromet l'intégrité de signal. La spécification de routage, rédigée par le concepteur avant toute opération de placement-routage, constitue le document de référence. Elle définit pour chaque classe de signal :

- Impédance cible et configuration de piste (microstrip, stripline, paire différentielle)

- Longueur maximale et minimale des traces, avec tolérance de length matching (par exemple +/- 0.6 mm entre bits d'un même byte DDR)

- Skew maximal entre signaux d'un même groupe (contraintes de timing)

- Couches de routage assignées pour les signaux les plus sensibles.

- Type et nombre de vias, longueur de stub maximale (back-drilling si nécessaire)

- Règles d'espacement pour limiter le crosstalk entre pistes adjacentes.

Le principe fondamental : router par ordre de criticité, du signal le plus contraint au moins contraint. Les paires différentielles haute vitesse (PCIe, USB 3, HDMI) sont routées en premier, suivies des bus mémoire (DDR), puis des signaux basse vitesse. Sur des outils comme Cadence Allegro ou Altium Designer, les contraintes d'impédance et de length matching sont paramétrées dans le constraint manager pour un contrôle automatique en temps réel. Pour les applications vidéo industrielle intégrant HDMI, SDI ou des interfaces propriétaires, notre comparatif des protocoles vidéo haute résolution pour l'industrie détaille les contraintes de routage spécifiques à chaque standard.

Un point souvent sous-estimé : le routage en impédance contrôlée est une condition nécessaire mais insuffisante. La continuité du plan de référence sous chaque piste haute vitesse, l'absence de changement de couche de référence sans via de découplage, et la gestion des retours de courant sont tout aussi critiques.

5. Simulations d'intégrité de signal (SI) et d'alimentation (PI)

La simulation est l'outil qui transforme une conception probable en conception garantie. Dans notre lab, nous utilisons régulièrement les outils ANSYS, Signal Integrity, Power Integrity, simulation digitale haute vitesse et optimisation d'antennes assistée par IA. Cette combinaison permet de dire, avant fabrication et avec une bonne précision, si une carte va fonctionner, ou d'identifier précisément les violations à corriger avant gravure. Nous déterminons le niveau de simulation nécessaire en fonction du risque technique et du volume de production visé.

Signal Integrity (SI)

La simulation d'intégrité de signal vérifie que chaque canal de transmission respecte son budget de pertes et ses marges temporelles. En pré-layout, elle valide les choix de stack-up et de topologie. En post-layout, elle intègre la géométrie réelle des pistes extraite du PCB routé. Nous travaillons selon Ansys, éditeur de la suite SIwave, en extrayant les parasites post-layout et en alimentant le solveur avec les modèles IBIS/AMI fournis par les fabricants, c'est cette combinaison que nous utilisons pour valider chaque canal critique avant gravure.

Pour les interfaces au-delà de 10-12 Gbps (PCIe Gen4, USB4, Ethernet 25G), la simulation post-layout avec extraction 3D devient indispensable. En dessous de ce seuil, un ingénieur expérimenté disposant d'un stack-up validé et de règles de routage strictes peut se passer de simulation complète, à condition de maîtriser parfaitement le budget de pertes du canal.

Power Integrity (PI)

L'intégrité d'alimentation est un facteur de réussite souvent négligé. Une alimentation peut sembler fonctionnelle tout en présentant des déficiences qui dégradent les performances des transceivers haute vitesse. Les variations de tension sur les rails d'alimentation (ripple, bruit de commutation) affectent directement le jitter et les marges temporelles des signaux.

La simulation PI se décline en deux volets complémentaires :

- PI DC (statique) : vérifie l'uniformité de la distribution de tension (IR drop) sur l'ensemble du plan d'alimentation. Un DC-drop excessif entre le régulateur et les broches d'un FPGA peut provoquer des dysfonctionnements intermittents.

- PI AC (dynamique) : valide que le réseau de découplage (capacités de bypass) fournit une impédance suffisamment basse sur toute la plage de fréquences de fonctionnement. Le dimensionnement correct des capacités de découplage, de leur placement et de leurs interconnexions est essentiel.

Ces simulations, réalisées avec des outils comme ANSYS SIwave ou Cadence Sigrity, sont systématiques sur les cartes complexes et indispensables sur les designs intégrant des FPGA ou des SoC haute performance.

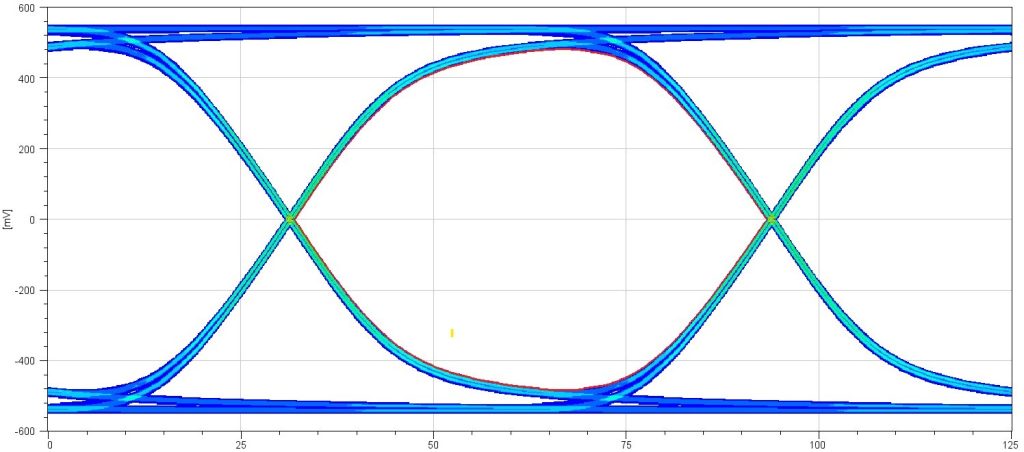

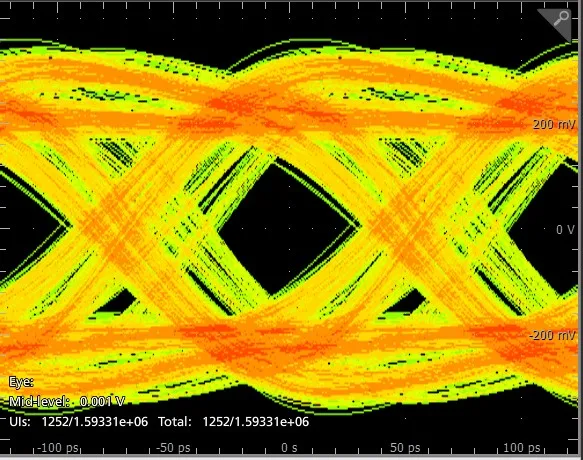

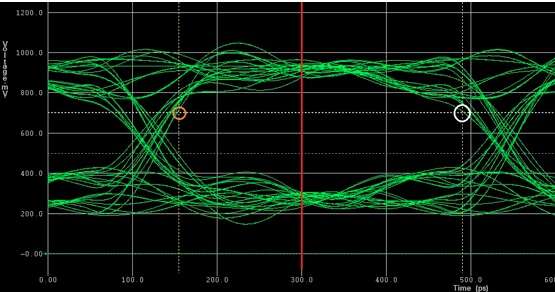

Diagramme de l'oeil et validation

Le diagramme de l'oeil (eye diagram) est l'indicateur synthétique de la qualité d'un canal de transmission. Il superpose les transitions du signal pour visualiser les marges en tension et en temps. Un oeil largement ouvert indique un canal sain ; un oeil qui se ferme signale des pertes excessives, du jitter ou des réflexions.

La corrélation entre simulation et mesure est une étape clef. Un eye diagram simulé dans des conditions idéalisées (température nominale, alimentation parfaite) ne reflète pas le comportement en production. Dans notre pratique, nous simulons systématiquement aux corners (température haute, tension basse, pire cas de variation process) pour garantir des marges suffisantes sur l'ensemble de la plage de fonctionnement.

Horloges et jitter

Les horloges sont à la fois les signaux les plus critiques et les plus susceptibles de polluer leur environnement. Le jitter (instabilité temporelle du front d'horloge) est un paramètre déterminant pour les interfaces haute vitesse : un jitter excessif réduit directement les marges temporelles du diagramme de l'oeil. La sélection de l'oscillateur, la qualité du réseau de distribution (fanout buffers, terminaisons) et l'isolation par rapport aux sources de bruit doivent être traitées avec le plus grand soin.

Equaliseurs et pré-emphasis

Les équaliseurs intégrés dans les transceivers modernes compensent les pertes du canal de transmission en amplifiant sélectivement les hautes fréquences. Les transceivers PCIe Gen4/Gen5, USB 3.2 et Ethernet intègrent des algorithmes d'adaptation automatique (CTLE, DFE) qui ajustent leurs paramètres en fonction du canal réel. Lorsque l'adaptation n'est pas automatique, la configuration de ces paramètres nécessite une collaboration étroite entre le concepteur hardware et le développeur firmware.

Un point pratique important : les équaliseurs rendent la mesure directe à l'oscilloscope impossible sans fonction de démodulation intégrée. La validation en laboratoire des liens haute vitesse équalisés requiert un oscilloscope avec logiciel de conformité dédié.

6. Prototype et validation

La validation d'un prototype haute vitesse ne se limite pas à constater que le système démarre. Elle implique des tests de conformité rigoureux : compliance PCIe, JEDEC pour DDR, certification USB-IF. Nous avons réalisé des passages de compliance PCIe endpoint sur des produits clients, validant la conformité du lien série aux spécifications du standard.

Ces tests de conformité utilisent les mêmes algorithmes et masques que ceux employés par les concepteurs de puces. Ils révèlent des non-conformités que le fonctionnement nominal masque, mais qui se manifestent en production face aux dispersions de composants et aux variations de température.

7. Industrialisation et vie série

La transition du prototype à la production série est une phase critique pour les conceptions haute vitesse. L'intégrité de signal validée sur un prototype peut se dégrader en série si le suivi de fabrication n'est pas rigoureux : variations de l'épaisseur diélectrique entre lots, dérive des impédances, qualité de gravure des pistes. Nous accompagnons nos clients dans cette phase en définissant les critères d'acceptation PCB (coupon de test d'impédance, microsection) et les procédures de contrôle en réception. Notre approche DFM intègre ces contraintes dès la conception pour éviter les surprises en phase d'industrialisation.

FR4 vs Rogers : comment arbitrer le choix matériau ?

Le choix du matériau PCB découle directement du budget de pertes canal et de la plage de fréquences. FR4 standard (JEDEC-compatible, εr 4,4, Df 0,020 @ 1 GHz, Tg 130 °C) convient jusqu'à 2 GHz. FR4 High-Tg / Isola 370HR (Tg 180 °C) monte à 5 GHz en canal court. Megtron 6 (Df 0,004 @ 12 GHz) et Tachyon 100G (Df 0,0021) sont le standard pour PCIe Gen 4/Gen 5 (16–32 GT/s). Rogers RO4350B reste la référence mixte RF-numérique : εr = 3,48, stable de -40 °C à +125 °C avec une dérive < 50 ppm/°C, ce qui est décisif quand on pose des antennes imprimées à proximité de bus DDR.

Conformément à IEEE 802.3, les canaux 10GbE imposent une perte d'insertion canal totale < 6 dB à la fréquence de Nyquist (2,5 GHz), ce qui interdit le FR4 standard sur plus de ~20 cm. PCIe Gen 5 (Nyquist 16 GHz) exige < 30 dB canal total, seuls Megtron 6/7 et équivalents tiennent ces contraintes sur des backplanes réalistes. D'après le PCI-SIG, les masques de compliance PCIe 5.0 et 6.0 documentent précisément les gabarits d'œil à respecter. Les timings DDR5 (jusqu'à 6400 MT/s avec tCK ≈ 312 ps) sont définis selon Jedec dans le standard JESD79-5, et comme le souligne Micron dans ses notes d'application sur les interfaces DDR5, la marge de read/write leveling n'est tenable que si le length matching différentielle reste dans la fenêtre de ±0,4 mm pour chaque byte lane.

Notre service d'audit de bus numériques

L'audit de bus numériques par diagrammes de l'oeil est l'une de nos capacités centrales. Nous avons audité de nombreux bus clients, DDR, PCIe, USB 3.x, HDMI, LVDS, avec des résultats tranchés : certains bus passent largement dans le masque de conformité, d'autres révèlent des marges insuffisantes invisibles en fonctionnement nominal mais fatales en production série. Cette capacité de diagnostic transforme une intuition de problème en données quantifiées exploitables pour la reprise de design.

Notre portfolio haute vitesse couvre concrètement : PCIe jusqu'à Gen 5, DDR2/3/4 et LPDDR4, USB 2.0/3.0/3.2, SDI, HDMI 2.0, LVDS, MIPI-CSI/DSI et SATA. Au Q1 2026, nous avons livré un projet Jetson Orin NX avec interface LPDDR4x native et BSP Yocto customisé, ainsi qu'un ordinateur industriel custom à base d'Intel i5 avec architecture PCIe multi-lanes. Côté radiofréquence, notre portfolio s'étend jusqu'à 10 GHz, ce qui nous permet de traiter les projets mixtes numérique/RF sans rupture de compétence.

Retour terrain : sur un projet LIDAR techniquement exigeant, nous avons mesuré des eye diagrams post-fabrication qui corrélaient à mieux que 10 % avec nos simulations SI pré-layout (ANSYS SIwave + modèles IBIS/AMI STMicroelectronics et Nordic), un niveau de corrélation qui permet d'engager la production série sans respin PCB. À l'inverse, sur un bus DDR audité chez un client, nous avons constaté une ouverture verticale d'œil ramenée à 80 mV en coin haute température (vs 150 mV nominal), révélant un budget de marge insuffisant invisible à température ambiante. Ces observations illustrent un principe que nous appliquons systématiquement : simuler et valider aux corners (conforme aux catégories IPC-6012 classe 2/3), pas seulement en conditions nominales.

Pour les synchronisations d'horloge multi-cartes, nous appliquons les recommandations IEEE 1588 (PTP) et cadrons les stack-ups conformément à l'IPC-2221 classe 2 ou classe 3 selon la criticité. Les chipsets typiquement intégrés incluent STM32 Cortex-M7, NXP i.MX8 Cortex-A53/A72, et sur le haut de gamme NVIDIA Jetson Orin NX avec LPDDR4x et liens PCIe Gen 4.

Cas concret : sur un projet industriel récent, nous avons conçu un ordinateur sur mesure à base d'Intel i5 avec une architecture PCIe densément peuplée. Contrairement à l'idée qu'un FR4 haut de gamme suffit pour PCIe Gen 4, malgré un canal court, nous avons opté pour Megtron 6 après simulation SI sous ANSYS HyperLynx et SIwave, l'écart d'insertion loss mesuré entre FR4 amélioré et Megtron était de 3 dB à 8 GHz, suffisant pour fermer l'œil PCIe sur le cas le plus défavorable. À l'inverse, pour un bus DDR3 audité chez un client, le FR4 High-Tg a parfaitement tenu le budget de pertes, prouvant qu'il n'y a pas de matériau "meilleur", seulement un matériau adapté au budget canal. Les plateformes firmware ciblées sur ces designs incluent typiquement Zephyr ou FreeRTOS pour les contrôleurs auxiliaires et Yocto pour les applications Linux embarquées.

Pourquoi choisir AESTECHNO pour vos projets haute vitesse

La conception haute vitesse exige une combinaison rare de compétences : maîtrise de l'électromagnétisme, connaissance intime des protocoles série, expérience de l'industrialisation. Notre équipe réunit ces compétences au sein d'une pratique qui couvre des systèmes intégrant des millions de portes logiques, dissipant des centaines de watts et transmettant des données à des dizaines de Gbps.

Notre différenciateur tient en trois points :

- Chaîne complète maîtrisée : du schéma au stack-up, du routage aux simulations SI/PI, du prototype à l'industrialisation. Pas de sous-traitance, pas de rupture de compétence entre les étapes.

- Approche right-first-time : chaque choix technique est validé par simulation ou par l'expérience acquise sur des projets comparables. L'objectif est un prototype fonctionnel dès la première itération.

- Vision industrielle : nous ne concevons pas un prototype qui fonctionne en laboratoire. Nous concevons un produit qui fonctionne en production, sur toute sa plage de température, avec la variabilité réelle des composants et des PCB.

En tant que bureau d'études électronique basé à Montpellier, nous accompagnons nos clients sur l'ensemble du cycle de vie de leurs produits haute performance.

Pourquoi choisir AESTECHNO pour le high-speed ?

- 10+ ans d'expertise en conception haute vitesse : DDR4, DDR5, LPDDR4, PCIe, USB 3, HDMI.

- Projets DDR5 et PCIe réalisés avec compliance validée.

- Approche right-first-time : simulations SI/PI systématiques, validation aux corners.

- Chaîne complète : schéma, stack-up, routage, simulation, industrialisation.

- Bureau d'études français basé à Montpellier.

Article rédigé par Hugues Orgitello, ingénieur en conception électronique et fondateur d'AESTECHNO. Formateur CAP'TRONIC sur la formation Introduction à la conception de cartes pour signaux High-Speed. Profil LinkedIn.

En résumé : ce qui fait la différence en conception haute vitesse

La conception haute vitesse n'est pas une option stylistique mais une discipline mesurable. Les vrais gagnants sont les projets où le stack-up est figé avant la première piste, où les impédances sont contrôlées à ±10% classe 2 (ou ±5% classe 3 pour PCIe Gen 5 et DDR5), où les simulations SI/PI sont réalisées avant gravure et où les marges sont validées aux corners (température, tension, variations process). Les échecs que nous auditons partagent un schéma commun : un stack-up choisi tardivement, un matériau FR4 standard sur un canal qui dépasse son budget de pertes, et des paires différentielles sans length matching strict.

Notre portfolio couvre PCIe jusqu'à Gen 5 (32 GT/s), DDR4/5 et LPDDR4x, USB 2.0 à 3.2, HDMI 2.1, 10GbE et antennes jusqu'à 10 GHz. La signature : right-first-time, un prototype qui fonctionne dès la première itération, parce que chaque décision a été validée avant gravure par simulation ou par retour d'expérience documenté. Contactez-nous pour un audit ciblé de votre canal critique.

Projet haute performance ? Audit gratuit 30 min

Discutons de vos contraintes d'intégrité de signal, de stack-up et de simulation. Nous vous donnons un avis technique concret en 30 minutes.

- Revue de stack-up et choix matériaux (FR4, Megtron, Rogers)

- Pré-audit compliance PCIe / JEDEC DDR / USB-IF.

- Analyse eye diagram et budget de pertes canal.

Audit gratuit 30 min | contact@aestechno.com

FAQ : Conception haute vitesse et intégrité de signal

Quelle est la différence entre conception standard et haute vitesse ?

En conception standard, les pistes du PCB se comportent comme de simples connexions filaires. En haute vitesse, elles deviennent des lignes de transmission dont l'impédance caractéristique, les pertes et les réflexions conditionnent le fonctionnement du système. La frontière se situe typiquement lorsque le temps de montée du signal est inférieur au double du temps de propagation sur la piste. En pratique, tout signal au-delà de 50 MHz ou dont le temps de montée est inférieur à 1-2 ns relève du design haute vitesse et nécessite une impédance contrôlée, un stack-up dédié et potentiellement des simulations d'intégrité de signal.

À partir de quel débit faut-il un design haute vitesse ?

Il n'existe pas de seuil universel, car c'est le temps de montée du signal, et non sa fréquence fondamentale, qui détermine la nécessité d'un traitement high-speed. Cependant, en pratique, les interfaces suivantes nécessitent systématiquement un design haute vitesse : DDR3 et au-delà (à partir de 1600 MT/s), PCIe toutes générations (2.5 GT/s et plus), USB 3.0 et supérieur (5 Gbps), HDMI 1.4 et supérieur, Ethernet gigabit et au-delà. Même un bus I2C rapide (3.4 MHz) peut nécessiter une attention particulière sur les temps de montée si les longueurs de piste sont importantes.

Quels matériaux PCB pour les signaux supérieurs à 5 Gbps ?

Au-delà de 5 Gbps, le FR4 standard (facteur de dissipation Df d'environ 0.02) introduit des pertes diélectriques qui peuvent fermer le diagramme de l'oeil. Les alternatives, classées par niveau de performance croissant : FR4 amélioré (Df 0.010-0.015) comme l'IS415 de Isola, matériaux mid-loss (Df 0.005-0.008) comme le Megtron 4, et matériaux ultra-faible perte (Df inférieur à 0.005) comme le Megtron 6 ou le Tachyon 100G. Le choix du matériau se fait en arbitrant entre performance, coût de fabrication et disponibilité. AESTECHNO réalise cette analyse en pré-layout pour chaque projet, en calculant le budget de pertes du canal complet.

Comment garantir le right-first-time en high speed ?

Le right-first-time repose sur quatre piliers : un cadrage technique rigoureux qui identifie les risques avant la conception, un stack-up validé par simulation et co-défini avec le fabricant PCB, un routage conforme à une spécification détaillée avec contrôle d'impédance et de length matching, et des simulations SI/PI adaptées au niveau de risque du projet. Nous appliquons cette méthodologie de manière systématique. La simulation aux corners (température, tension, variations process) et la corrélation avec des mesures en laboratoire complètent cette approche pour garantir le fonctionnement en production et non seulement sur le prototype.

AESTECHNO peut-elle prendre en charge un projet DDR5/PCIe ?

Oui : notre équipe dispose de l'expertise et des outils nécessaires pour mener un projet DDR5 ou PCIe de bout en bout : architecture système, définition du stack-up avec matériaux adaptés, routage sous contraintes strictes (length matching, impédance différentielle), simulations SI et PI pré et post-layout, validation par diagramme de l'oeil, et accompagnement à l'industrialisation. Nous avons réalisé des passages de compliance PCIe endpoint et maîtrisons les contraintes spécifiques de la DDR5 (décision feedback equalization, power integrity renforcée). Contactez-nous à contact@aestechno.com pour discuter de votre projet.

Articles connexes

Pour approfondir les sujets liés à la conception haute performance :

- DDR4 vs DDR5 : comparatif technique et contraintes de routage.

- LPDDR4 : secrets et performance des interfaces mémoire mobiles.

- Conception de cartes FPGA : interfaces haute vitesse et transceivers.

- Conception de cartes RF et certification radio.

- DFM : Design for Manufacturing en électronique.

- Bureau d'études électronique AESTECHNO.