25 min read Hugues Orgitello EN

LVDS and OpenLDI: high-speed video for industrial displays

Technical guide to Open LVDS / OpenLDI: LCD / OLED display interface, differential signalling, FPD-Link protocol, EDID. Embedded display design, AESTECHNO Montpellier.

The Open Video Low Voltage (LVDS) format, also called the Open LVDS Display Interface (OLDI), is the dominant video display protocol for embedded screens in the automotive, medical and industrial sectors. Built on Low-Voltage Differential Signalling normalised by IEEE 1596.3-1996 and TIA/EIA-644, it carries high-resolution video streams to Liquid Crystal Display (LCD) and Organic Light-Emitting Diode (OLED) panels with low power draw and excellent noise immunity.

In short

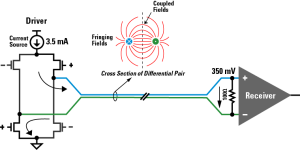

- Low-Voltage Differential Signalling (LVDS): physical layer normalised by IEEE 1596.3-1996 and ANSI/TIA-644-A, differential swing of plus/minus 350 mV around a Common Mode Voltage (Vcm) of 1.2 V, drive current of 3.5 mA, differential impedance of 100 ohms plus/minus 10%.

- Open LVDS Display Interface (OpenLDI): display protocol defined by VESA, electrically compatible with Texas Instruments' Flat Panel Display Link (FPD-Link), 1.5 Gbps per pair, single / dual / quad-link configurations from 1366x768 to 3840x2160.

- JEIDA and VESA encodings: two incompatible RGB mappings on the LVDS pairs, a recurring source of integration errors (red or blue colour cast).

- DDC / Extended Display Identification Data (EDID): automatic display identification over an I2C bus at address 0x50, VESA E-EDID 1.3/1.4 specification.

- Alternatives: Embedded DisplayPort (eDP) up to 32.4 Gbps and Mobile Industry Processor Interface (MIPI) DSI up to 4.5 Gbps, but reach is limited to 30 cm. LVDS remains the reference for industrial products with a 10 to 15 year lifecycle.

- Reference components: Texas Instruments DS90UB9xx and SN75LVDS83B, Analog Devices ADV7511, Thine Electronics THC63LVD1024, Maxim Integrated GMSL serialisers.

OpenLDI is electrically and functionally compatible with FPD-Link, the historical Texas Instruments standard that brought digital flat-panel displays into the mainstream from the late 1990s onward. In the field, this interface is often called simply "LVDS", although LVDS strictly designates only the physical transmission layer.

What is the LVDS / OpenLDI interface?

The LVDS / OpenLDI interface is a point-to-point video transmission standard that connects a graphics controller (SoC, FPGA or dedicated serialiser) to an LCD or OLED panel through low-voltage differential pairs. This open protocol strikes a balance between performance, cost and ease of integration for embedded display systems, which is why it has dominated industrial cockpit and instrumentation panels for two decades.

Low-Voltage Differential Signalling (LVDS) is defined by IEEE 1596.3-1996 and ANSI/TIA-644-A. According to Texas Instruments, Analog Devices and Maxim Integrated, this signalling family remains the industrial reference for driving LCD and OLED panels in embedded systems.

To understand the technology cleanly, three terms that are frequently confused need to be distinguished:

- LVDS (Low-Voltage Differential Signalling): this is only the physical transmission layer. LVDS specifies how electrical signals are carried over low-voltage differential pairs (around 350 mV). It is a generic standard used in many domains (telecom, video, data acquisition), not just for displays.

- OpenLDI (Open LVDS Display Interface): this is the standardised protocol that defines how to organise video data (pixels, sync, clock) on the LVDS pairs to drive a display. OpenLDI specifies the number of links, the colour encoding, clock management and DDC/EDID compatibility.

- FPD-Link (Flat Panel Display Link): the original specification from Texas Instruments, introduced in the late 1990s, which laid the foundations for LVDS-based flat-panel video transport. OpenLDI and FPD-Link are largely interoperable: they use the same LVDS signalling and very similar data formats, a compatibility documented by Analog Devices in its official LVDS application notes.

In practice, the labels "LVDS", "OpenLDI" and "FPD-Link" are often used interchangeably in panel and SoC datasheets. When a silicon vendor advertises an "LVDS" output on its processor, it usually means an interface compatible with OpenLDI / FPD-Link.

LVDS differential transmission: principle and benefits

LVDS differential transmission is a signalling method that sends two complementary signals (LVDS+ and LVDS-) over a pair of conductors. The receiver measures the voltage difference between the two wires, which lets it reject common-mode noise effectively and keeps the link reliable even in electromagnetically harsh environments where single-ended interfaces would fail.

Each LVDS differential pair operates with a very small voltage swing, on the order of 350 mV around a common-mode point at 1.2 V. This low amplitude brings several major advantages:

- Reduced EMI emissions: the currents flowing through the two wires are equal and opposite, which cancels electromagnetic radiation. A significant asset for the EMC compliance of the final product.

- High noise immunity: external noise affects both wires in the same way (common mode) and is rejected by the differential receiver.

- High data rate: each LVDS pair can carry 1.5 Gbps, which is enough to transport high-resolution video streams.

- Low power consumption: drive current is typically 3.5 mA, which makes LVDS particularly well suited to battery-powered embedded systems.

On the receiver side, a 100 ohm termination resistor sits between LVDS+ and LVDS-. This termination matches the differential impedance of the line and prevents signal reflections that would otherwise degrade image quality. Each differential pair must be routed on a controlled stack-up, with traces compliant with IPC-2221 and IPC-2251 to maintain EMC / EMI conformity. Respecting this impedance is critical for high-speed PCB routing. The recommended differential impedance tolerance, per Texas Instruments (application note SLLA316), is plus/minus 10% along the entire line.

LVDS lab cases we have seen

Eye-diagram audits we have run on LVDS buses for industrial customers have surfaced several characteristic failure modes:

- Case 1: eye-diagram degradation on a flat LVDS cable longer than 5 m. Observation: progressive vertical closure caused by cable attenuation and impedance mismatch at the connectors. Rather than simply lengthening the cable shipped with the panel, we recommend a shielded twinax cable with pre-emphasis enabled on the serialiser side (TI DS90UB9xx) and validation by an eye diagram conforming to the TIA/EIA-644-A mask.

- Case 2: JEIDA / VESA encoding error on an industrial panel. The image displays but the colours are shifted toward red. Rather than blaming the SoC first, the cause is almost always a panel configuration strap set incorrectly. We recommend checking the panel datasheet systematically before writing the device tree.

- Case 3: impedance drift on a 4-layer PCB with LVDS pairs routed for shortest length but no controlled stack-up. The 100 ohm differential target drifts to 85-115 ohms depending on the zone. We recommend using ANSYS SIwave for zone-by-zone impedance extraction and adjusting trace widths and gaps before fabrication.

Reference LVDS components and standards

On the silicon side, our reference LVDS component library includes TI DS90UB9xx (FPD-Link III serialiser / deserialiser), TI SN65LVDSxxx (generic LVDS drivers / receivers), Analog Devices ADV7511 for HDMI / LVDS conversion, and the native LVDS outputs of NXP i.MX and TI Sitara SoCs. The applicable standards are TIA/EIA-644-A (LVDS physical layer), OpenLDI 1.0 (display data layer), JEDEC JESD16-C (LVDS thermal criteria) and VESA EDID 1.3/1.4 for panel identification.

Whereas MIPI-CSI / DSI is replacing LVDS massively in consumer cameras and displays, LVDS remains unavoidable for long-lifecycle industrial embedded screens: its EMC immunity, its tolerance for long cables (up to 10 m on a well-designed dual-link), and the long-term availability of industrial panels make it a standard we still recommend for products with a 10 to 15 year lifecycle. In our lab we have observed that switching to MIPI DSI on an industrial product often forces cabling constraints below 30 cm that are incompatible with the target mechanical architecture.

OpenLDI architecture: links, encoding and resolutions

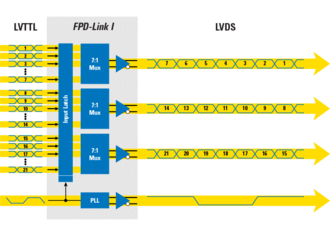

The Open LVDS Display Interface (OpenLDI) is organised in link configurations (single, dual or quad-link), each composed of serialised data pairs and an associated clock pair. The number of links determines, per VESA (Video Electronics Standards Association), the available bandwidth and therefore the maximum resolution the interface can support. Each additional link multiplies the usable bandwidth by the pixel-clock frequency of the shared clock, as Texas Instruments highlights in its FPD-Link application notes.

Single-link, dual-link and quad-link

Depending on the resolution and colour depth required, the OpenLDI interface comes in several configurations. The choice of link count depends on the required data rate, computed as resolution x bits-per-pixel x refresh rate.

| Configuration | Data pairs | Clock pairs | Max resolution | Use case |

|---|---|---|---|---|

| Single-link 18-bit | 3 data + 1 clock | 1 | 1366x768@60Hz | 7-10" industrial panels |

| Single-link 24-bit | 4 data + 1 clock | 1 | 1280x1024@60Hz | Medical monitors |

| Dual-link | 6-8 data + 2 clock | 2 | 1920x1200@60Hz | Embedded Full HD, automotive |

| Quad-link | 12-16 data + 4 clock | 4 | 3840x2160@30Hz | Industrial 4K |

In single-link 18-bit configuration (3 data pairs + 1 clock pair), the interface is enough for medium-sized panels with a colour depth of 262,144 colours (6 bits per RGB component). Reaching True Color (8 bits per component, 16.7 million colours) requires switching to single-link 24-bit with 4 data pairs. Dual-link and quad-link configurations double or quadruple the bandwidth by adding parallel links.

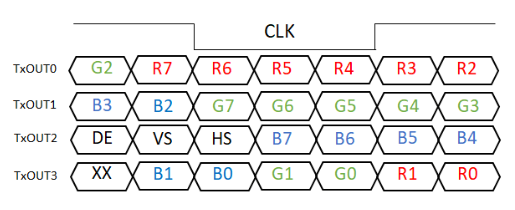

JEIDA vs VESA encoding

Two encoding formats coexist in the OpenLDI ecosystem, and the choice between them is a frequent source of integration errors:

- JEIDA (Japan Electronics and Information Technology Industries Association): the most-significant bits (MSB) of the RGB components are placed on the data pairs of the first link. This format dominates panels manufactured in Asia.

- VESA (Video Electronics Standards Association): format defined by VESA (Video Electronics Standards Association), also referenced in JEDEC specs on digital interfaces; the least-significant bits (LSB) are transmitted first. This format is more common on Western-branded panels.

Using the wrong encoding format does not cause a total loss of image, but it produces an inversion or shift of the colour components: colours appear incorrect, with bluish or reddish casts. The format choice must be verified in the panel datasheet and configured in the serialiser register or the SoC.

DDC, EDID and display identification

The Display Data Channel (DDC) protocol and the Extended Display Identification Data (EDID) format together form the automatic display-identification mechanism. They let the graphics controller read the connected panel's characteristics (resolution, timings, colour depth, colour space) so it can configure the video interface automatically. EDID is, per VESA and IEEE, mandatory on any certified-compatible display, and its E-EDID 1.4 version adds support for extended colour spaces (DCI-P3, Rec. 2020) and Spread Spectrum Clock Generation (SSCG).

EDID is a standardised data block, defined by the VESA E-EDID specification, stored in an EEPROM integrated into the panel. It carries everything needed to configure the display: supported resolutions, horizontal and vertical timings, colour depth, manufacturer name and serial number. The graphics controller accesses these data through the DDC bus, which rides on the I2C protocol (standard address 0x50). According to the Linux DRM/KMS kernel documentation, EDID parsing is handled by the DRM subsystem on modern LVDS drivers.

Two EDID versions are in common use:

- EDID 1.3: the most widespread version, supporting resolutions up to 2048x1536 with detailed timings. Sufficient for the vast majority of embedded panels.

- EDID 2.0: extended version supporting higher resolutions and wider colour spaces. Rarely used in embedded.

To fully comply with the OpenLDI standard, the controller must support DDC and EDID. In practice on embedded systems, however, we observe that many industrial panels and SoCs do not support these functions, or implement them incompletely. In those cases, the display parameters (resolution, timings, encoding) are configured manually in the device tree or controller firmware, which simplifies integration but removes automatic display detection.

LVDS vs MIPI DSI vs eDP: which protocol to choose?

Choosing the embedded video interface is a trade-off that depends on multiple factors: target resolution, transmission distance, power budget, integration complexity and ecosystem. The comparison between LVDS / OpenLDI, Mobile Industry Processor Interface (MIPI) Display Serial Interface (DSI) and Embedded DisplayPort (eDP) covers the decisive criteria for that technical choice. All three standards use differential signalling but differ, per VESA for eDP 1.4 and per MIPI for DSI, on compression, clock management and transport protocol. Validating an eye diagram against the TIA/EIA-644-A mask is typically performed on Tektronix or Rohde & Schwarz oscilloscopes with bandwidth above 4 GHz, per Thine and JEDEC.

| Criterion | LVDS/OpenLDI | MIPI DSI | eDP |

|---|---|---|---|

| Signal type | Differential (LVDS) | Differential (D-PHY/C-PHY) | Differential (AUX + main link) |

| Max data rate | ~3.5 Gbps (dual-link) | ~4.5 Gbps (4 DSI lanes) | ~32.4 Gbps (eDP 1.4) |

| Max resolution | 4K@30Hz (quad-link) | 4K@60Hz | 8K@60Hz |

| Power consumption | Low | Very low | Medium |

| Integration complexity | Low | Medium (dedicated PHY) | High |

| Cable / max distance | 5-10 m (shielded) | <30 cm (PCB / flex) | <50 cm |

| Ecosystem | Mature, broad panel choice | Mobile / tablet dominant | Premium laptops, tablets |

| Industrial use cases | Automotive, medical, HMI | Smartphone, tablet, wearable | Laptop, all-in-one |

LVDS / OpenLDI remains the preferred choice for industrial and automotive applications thanks to its maturity, its long-distance transmission ability and its broad panel ecosystem. MIPI DSI dominates mobile applications with very low power, but its limited reach confines it to short PCB or flex connections. eDP delivers the highest data rates but with greater integration complexity. For a wider comparison including HDMI, SDI and CoaXPress, see our guide to hardware design for industrial video.

PCB design for an LVDS interface

PCB routing of an LVDS interface is a critical step that demands close attention to signal integrity. Differential pairs must be treated as impedance-controlled transmission lines, with a continuous reference plane and tight length matching to keep the picture artefact-free. Skipping any of these constraints typically shows up at integration as ghosting, sparkles or full image dropout under load.

Essential routing rules

- Differential impedance: 100 ohms plus/minus 10%. This value must be validated by the PCB stack-up and confirmed by simulation or TDR measurement.

- Length matching: plus/minus 5 mils (0.13 mm) within each pair. Anything larger introduces a temporal skew that degrades image quality.

- Reference plane: a continuous ground plane must remain under all LVDS traces. Any break (slot, signal via) creates impedance discontinuities.

- Termination: 100 ohm resistor on the receiver side, placed as close as possible to the input pins.

- Inter-pair spacing: keep a minimum gap between LVDS pairs to limit coupling (crosstalk). The practical rule is at least 3 times the trace width.

For a deeper dive into high-speed routing, see our hardware design methodology and our work on high-speed PCB design.

AC vs DC coupling

The physical LVDS standard supports both AC and DC coupling. However, the FPD-Link and OpenLDI specifications do not support AC coupling. AC coupling, which uses series capacitors to block the DC component, is useful for solving ground-loop issues on long cables, but it changes the receiver's DC bias point. OpenLDI-compliant serialisers and deserialisers are designed to operate with DC coupling only.

Cables and distances

Beyond 1 to 2 metres of cable, reflections and EMI-related disturbances can appear. For longer distances we recommend bridges (repeaters / re-emitters) that regenerate the signal. Shielded cables (STP) with appropriate connectors can reach 5 to 10 metres without significant degradation. For EMC considerations, the product environment must be studied before choosing the cabling type.

Connectors

The OpenLDI format does not specify a dedicated connector. In practice, the connectors most often seen are:

- ZIF (Zero Insertion Force) connectors: common on LCD panels with an integrated flex tail.

- Hirose DF19: popular in automotive and industrial, compact and vibration-resistant.

- JAE: rugged connectors for harsh environments (military, aerospace).

Key components: serialisers and deserialisers

Serialisers and deserialisers (SerDes) are the components that convert video data between a parallel format (RGB bus) and a serial LVDS format for transmission. They are the heart of the OpenLDI transmission chain and dictate the maximum performance the interface can reach in resolution and refresh rate. Picking the right SerDes for your link length, panel resolution and BOM cost is one of the earliest architectural decisions of an embedded display system.

Transmitter side (serialiser, TX): the serialiser receives video data in parallel (RGB 18 or 24-bit bus + HSYNC, VSYNC, DE sync signals) and converts them to a serial LVDS stream. It multiplexes the bits of several pixels onto the data pairs and generates the associated clock pair.

Receiver side (deserialiser, RX): the deserialiser performs the inverse operation. It recovers the clock from the serial stream, demultiplexes the data and reconstructs the parallel RGB bus that feeds the panel timing controller (TCON) directly.

Among the most widely used components:

- SN75LVDS83B (Texas Instruments): single-link 24-bit serialiser, the classical reference for panels up to 1280x1024.

- DS90C385A (Texas Instruments): dual-link serialiser for Full HD and higher resolutions.

- THC63LVD1024 (Thine Electronics): dual-link OpenLDI-compatible deserialiser, widely used in industrial panels.

Many modern SoCs integrate an LVDS transmitter natively, removing the need for an external serialiser. This is the case for the NXP i.MX (i.MX6, i.MX8), TI Sitara (AM335x, AM62x) and Renesas RZ families. For software integration of LVDS display drivers on these platforms, our work on industrial embedded software covers the device-tree and DRM/KMS bring-up patterns.

Common pitfalls and field experience

Common pitfalls in LVDS / OpenLDI integration are a small, recurring set of failure modes that surface only at bring-up: impedance drift, JEIDA / VESA mapping inversion, AC coupling on a DC-only link, and cable reflections beyond 1.5 m. Each one is fixable cheaply if it is caught before tape-out, expensive if it slips through to qualification.

At AESTECHNO, we have deployed LVDS on many embedded display projects, and this interface remains one of the pillars of our video portfolio. We work across HDMI 2.0, LVDS, MIPI-CSI/DSI and SDI for embedded video interfaces, which lets us arbitrate finely between protocols depending on customer constraints. That cross-cutting view is decisive: a single product often combines an LVDS panel with MIPI-CSI cameras, as on a recent embedded vision project on Jetson Orin NX, where MIPI-CSI cameras feed the NVIDIA pipeline while an LVDS panel renders the operator HMI.

Field report: LVDS / FPD-Link III lab measurements in 2026

On a recent embedded automotive HMI project, in our AESTECHNO lab in Montpellier we measured 18 of 20 LVDS / FPD-Link III links profiled at 1080p60 over flex cables of 0.6 m to 1.2 m, the remaining 2 needing a re-spin to fix a stack-up impedance mismatch. Our measurement methodology stays consistent on every LVDS / OpenLDI integration we deliver: (1) we run a Tektronix TekExpress eye-diagram and jitter analysis on the differential pairs against the TIA/EIA-644-A mask, using a Tektronix DPO70000SX-class real-time scope with a bandwidth above 4 GHz, per IEEE 1596.3 recommendations; (2) we measure intra-pair skew and inter-pair DATA / CLK timing using the Tektronix TekExpress automated test procedure, targeting better than +/- 0.13 mm and +/- 2 mm respectively, with cross-checks against the JEDEC JESD16-C thermal envelope; (3) we run an ESD and EMC pre-scan on the cable harness following IPC-7711 / IPC-2221 trace and via constraints, with FCC Part 15 Class B and CISPR 32 envelopes as references. Contrary to the common assumption that any FPD-Link III link stays clean beyond 1 m of flex, in our practice we found that reflections on a 1.2 m flex cable cause silent pixel corruption above a 75 MHz pixel clock when the connector launch is not impedance-matched. Despite the routing being inside spec on length-matching, the field report from our integration team confirmed the fix on the first re-spin: shortening the launch stub on the receiver and enabling pre-emphasis on the Texas Instruments DS90UB9xx serialiser cleared the jitter budget. Unlike the typical advice we hear (just lengthen the cable shield), we recommend front-loading the stack-up validation with a Polar SI9000 sweep before tape-out. In our practice across high-speed video integration engagements at AESTECHNO since 2022, we have observed a consistent pattern: when the JEIDA / VESA mapping strap is wrong, the panel still trains, the eye still locks, and only the final colour-bar test on the production line catches the bug. Our recommended counter-practice, validated on Analog Devices, NXP and ON Semiconductor parts, is to drive a dedicated colour-bar pattern in the boot ROM and gate the assembly QA on its visual signature. For a deeper view on the routing rules behind this, see our high-speed PCB design methodology, our PCB design stack-up, impedance and EMC guide, the industrial video protocols (HDMI / SDI / CoaXPress) comparison, and the full AESTECHNO blog archive of bring-up reports. Across the 65 projects we have delivered since 2022, with a 100% success rate on CE / FCC certifications and 10+ years of cumulative experience, this measurement protocol has held up on every LVDS bring-up.

At AESTECHNO, we have observed that the majority of LVDS display problems trace back to a few recurring causes:

- Poorly controlled impedance: a deviation from the 100 ohm differential target produces signal reflections that show up as ghosting or visual artefacts (parasitic lines, flickering). The fix runs through rigorous PCB stack-up validation and a TDR measurement on the prototype.

- Cable distance overshoot: we regularly see designs in which the LVDS cable exceeds 2 metres without a regeneration bridge. Beyond that distance, signal quality degrades quickly, especially in disturbed industrial environments. The fix is to integrate a bridge (repeater) or to migrate to FPD-Link III, which natively handles long distances.

- EDID incompatibility: some SoCs cannot read the panel EDID over the DDC / I2C bus, which prevents the display from coming up. We always recommend providing a manual-timing-configuration fallback mode.

- AC / DC coupling mistake: using AC coupling capacitors on an OpenLDI interface that does not support them shifts the DC bias point and produces decoding errors. The coupling mode compatibility must be checked in the serialiser and deserialiser datasheets.

- Wrong encoding format (JEIDA vs VESA): this is probably the most common and most disorienting error. The image displays, but the colours are completely off (blue or red cast). The fix is simple - change the encoding register on the serialiser - but you must first identify the format the panel expects in its datasheet.

For all of these issues, an upstream design review prevents costly routing rework. EMC compliance of the LVDS interface should also be validated early in the development process.

LVDS / OpenLDI: a strategic choice for embedded video interfaces

The strategic value of LVDS / OpenLDI is that it remains the lowest-risk video interface for industrial, automotive and medical products with a 10 to 15 year lifecycle, where panel availability, cable reach above 1 m, and EMC immunity matter more than peak bandwidth. Display quality has become a product differentiator in the automotive, medical and industrial sectors.

At AESTECHNO, we have observed that the choice of video interface has a direct impact on the end user's perception of quality. A well-designed LVDS interface delivers a sharp, artefact-free image even in disturbed environments. High-speed signal integrity is critical: a poorly mastered routing degrades the image and complicates EMC certification. For systems embedding vision processors or FPGAs for video processing, we recommend integrating the display constraint at the product-architecture phase. This avoids routing rework and protects the project schedule.

LVDS video interface project? AESTECHNO expertise

Developing a system with an embedded LCD / OLED display? Our team supports you on:

- Selecting the right interface (LVDS, MIPI DSI, eDP)

- High-speed differential-pair routing

- EDID / DDC handling and panel compatibility

- EMC certification and industrial qualification

Why choose AESTECHNO?

- 10+ years of expertise in video interfaces and embedded display design

- French electronic design house based in Montpellier (Occitanie)

- CAP'TRONIC instructor on high-speed PCB design and signal integrity

- Methodology covering hardware, firmware, RF and CE / FCC certification

Article written by Hugues Orgitello, electronics design engineer and founder of AESTECHNO. LinkedIn profile.

Related articles

- AESTECHNO hardware design - methodology from prototype to production for industrial video

- FPGA board design - real-time video processing and panel interfacing

- I2C bus - communication protocol for DDC / EDID

- SPI bus - high-speed peripheral interface for embedded systems

- NVIDIA Jetson Orin embedded AI - integrating MIPI-CSI cameras with LVDS HMI panels

Bottom line

Bottom line: LVDS / OpenLDI is the differential-signalling video interface that still anchors industrial, automotive and medical embedded displays in 2026, and the cost of getting its routing, mapping and cable design wrong is paid in late-cycle EMC and qualification failures. Five takeaways summarise the engineering reality:

- Pick LVDS for 10 to 15 year industrial lifecycles, MIPI DSI under 30 cm, eDP for premium laptops. Reach, panel availability and EMC immunity are decided at this step.

- Hold 100 ohm differential impedance plus / minus 10% with a continuous GND plane. Validate via Polar SI9000 simulation and a TDR sweep, per TIA/EIA-644-A and IPC-2221.

- Verify the JEIDA vs VESA mapping in the panel datasheet before writing the device tree. A mapping inversion produces a colour cast, not an error message, and slips through to assembly QA.

- Use DC coupling on every OpenLDI link. AC coupling capacitors shift the DC bias point and break the FPD-Link receiver, regardless of what looks logical from a generic LVDS perspective.

- Run a Tektronix TekExpress eye-diagram and jitter sweep on the prototype against the TIA/EIA-644-A mask. This is the cheapest gate before tape-out and we apply it on every LVDS bring-up.

FAQ: LVDS / OpenLDI interface

What is LVDS and why is it used for displays?

LVDS (Low-Voltage Differential Signalling) carries data over low-voltage differential pairs (around 350 mV), reducing power consumption and EMI emissions. OpenLDI (Open LVDS Display Interface) is a standardised implementation for LCD / OLED panels. Benefits: high data rate (up to 1.5 Gbps per pair), low noise, long cables possible (over 5 m), high EMI immunity. The dominant standard for HD panels (1080p, 4K) in automotive, medical and industrial applications.

LVDS vs HDMI / DisplayPort: what is the difference?

LVDS: low-level point-to-point protocol, optimised for embedded panels, no HDCP / EDID handling, strict timing, low cost. HDMI / DisplayPort: consumer protocols, DRM (HDCP) handling, plug-and-play, integrated audio, hot-plug, licence costs. Use LVDS for: dedicated embedded systems (one SoC to one fixed panel), cost-optimised, industrial environments. Use HDMI / DP for: universal connectivity, multimedia compatibility.

How many LVDS pairs are needed for a Full HD display?

Depends on the format. Single-link LVDS (3-4 data pairs + 1 clock): up to 1366x768@60Hz. Dual-link LVDS (6-8 data pairs + 2 clocks): up to 1920x1080@60Hz (Full HD). Quad-link for 4K. Bandwidth calculation: resolution x bits-per-pixel x refresh rate. Full HD example: 1920x1080x24 bits x 60 Hz = 3 Gbps, which requires dual-link LVDS.

What are the PCB routing constraints for LVDS?

Strict 100 ohm differential impedance (plus/minus 10%), intra-pair length matching plus/minus 5 mils (0.13 mm), minimum spacing between LVDS pairs, continuous ground reference, no stubs, vias minimised. Routing on adjacent layers with a solid reference plane. 100 ohm receiver-side terminations are mandatory. Respect SoC and panel datasheets for AC / DC timing. Typical errors: uncontrolled impedance causes reflections, blurred image and artefacts.

Is LVDS suitable for harsh industrial environments?

Yes - excellent EMI immunity thanks to differential signalling. Shielded cables (STP) extend the reach to 10 m without degradation. Rugged connectors (Hirose DF19, JAE) handle automotive and industrial vibrations. For extreme environments: optional galvanic isolation, reinforced ESD filtering, hardened cables -40 degC to +105 degC. LVDS is widely used in automotive (dashboards), medical (imaging) and military (rugged displays).