26 min de lecture Hugues Orgitello

Format Open Video LVDS : OpenLDI

Guide technique Open LVDS (OpenLDI) : interface affichage LCD/OLED, signaux différentiels, protocole FPD-Link, EDID. Conception écrans embarqués AESTECHNO.

Le format Open Vidéo Low Voltage (LVDS), ou Open Lvds Display Interface (OLDI), est le protocole d'affichage vidéo dominant pour les écrans embarqués dans les secteurs automobile, médical et industriel. Basé sur la signalisation Low Voltage Differential (LVDS) normalisée par IEEE 1596.3-1996 et TIA/EIA-644, il transmet des flux vidéo haute définition vers les écrans Liquid Crystal Display (LCD) et Organic Light Emitting Diode (OLED) avec une consommation réduite et une excellente immunité au bruit.

En résumé

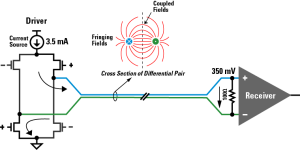

- Low-Voltage Differential Signaling (LVDS) : couche physique normalisée IEEE 1596.3-1996 et ANSI/TIA-644-A, swing différentiel ±350 mV autour d'un Common Mode Voltage (Vcm) de 1,2 V, courant de pilotage 3,5 mA, impédance différentielle 100 Ω ±10 %.

- Open LVDS Display Interface (OpenLDI) : protocole d'affichage défini par Vesa, électriquement compatible avec Flat Panel Display Link (FPD-Link) de Texas Instruments, débit 1,5 Gbps par paire, configurations single / dual / quad-link du 1366x768 au 3840x2160.

- Encodages JEIDA et Vesa : deux mappings RGB incompatibles sur les paires LVDS, source d'erreurs d'intégration récurrentes (dominante rouge ou bleue).

- DDC / Extended Display Identification Data (EDID) : identification automatique de l'écran via bus I2C à l'adresse 0x50, spécification Vesa E-EDID 1.3/1.4.

- Alternatives : Embedded DisplayPort (eDP) jusqu'à 32,4 Gbps et Mobile Industry Processor Interface (MIPI) DSI jusqu'à 4,5 Gbps, mais portée limitée à 30 cm. LVDS reste la référence pour produits industriels 10-15 ans.

- Composants de référence : Texas Instruments DS90UB9xx et SN75LVDS83B, Analog Devices ADV7511, Thine Electronics THC63LVD1024, Maxim Integrated GMSL sérialiseurs.

OpenLDI est électriquement et fonctionnellement compatible avec FPD-Link, le standard historique de Texas Instruments qui a démocratisé les écrans numériques à partir de la fin des années 1990. Dans l'industrie, cette interface est souvent appelée simplement "LVDS", bien que LVDS ne désigne en réalité que la couche physique de transmission.

Qu'est-ce que l'interface LVDS / OpenLDI ?

L'interface LVDS/OpenLDI est un standard de transmission vidéo point-à-point qui relie un contrôleur graphique (SoC, FPGA ou sérialiseur dédié) à un écran LCD ou OLED via des paires différentielles à basse tension. Ce protocole ouvert offre un équilibre entre performance, coût et facilité d'intégration pour les systèmes d'affichage embarqués.

Le Low-Voltage Differential Signaling (LVDS) est défini par les normes IEEE 1596.3-1996 et ANSI/TIA-644-A. cette signalisation reste, d'après Texas Instruments et selon Analog Devices et selon Maxim Integrated, la référence industrielle pour piloter les écrans Liquid Crystal Display (LCD) et Organic Light Emitting Diode (OLED) en embarqué.

Pour bien comprendre cette technologie, il est essentiel de distinguer trois termes souvent confondus :

- LVDS (Low Voltage Differential Signaling) : il s'agit uniquement de la couche physique de transmission. LVDS définit comment les signaux électriques sont transmis via des paires différentielles à basse tension (~350 mV). C'est un standard générique utilisé dans de nombreux domaines (télécom, vidéo, acquisition de données), pas seulement pour les écrans.

- OpenLDI (Open LVDS Display Interface) : c'est le protocole standardisé qui définit comment organiser les données vidéo (pixels, synchronisation, horloge) sur les paires LVDS pour piloter un écran. OpenLDI spécifie le nombre de liens, l'encodage des couleurs, la gestion de l'horloge et la compatibilité DDC/EDID.

- FPD-Link (Flat Panel Display Link) : c'est la spécification originale de Texas Instruments, apparue à la fin des années 1990, qui a posé les bases de la transmission vidéo sur LVDS pour les écrans plats. OpenLDI et FPD-Link sont largement compatibles : ils utilisent le même type de signalisation LVDS et des formats de données très similaires, compatibilité confirmée selon Analog Devices dans ses notes d'application LVDS officielles.

Dans la pratique, les termes "LVDS", "OpenLDI" et "FPD-Link" sont souvent utilisés de manière interchangeable dans les datasheets d'écrans et de SoC. Lorsqu'un constructeur annonce une sortie "LVDS" sur son processeur, il fait généralement référence à une interface compatible OpenLDI/FPD-Link.

Transmission différentielle LVDS : principe et avantages

La transmission différentielle LVDS est une méthode de signalisation qui consiste à envoyer deux signaux complémentaires (LVDS+ et LVDS-) sur une paire de conducteurs. Le récepteur mesure la différence de tension entre les deux fils, ce qui permet de rejeter efficacement le bruit de mode commun et de garantir une communication fiable même dans des environnements électromagnétiques perturbés.

Chaque paire différentielle LVDS fonctionne avec une excursion de tension très faible, de l'ordre de 350 mV autour d'un point de mode commun de 1,2 V. Cette faible amplitude présente plusieurs avantages majeurs :

- Réduction des émissions EMI : les courants circulant dans les deux fils sont égaux et opposés, ce qui annule le rayonnement électromagnétique. C'est un atout considérable pour la conformité CEM des produits.

- Haute immunité au bruit : le bruit externe affecte les deux fils de manière identique (mode commun) et est rejeté par le récepteur différentiel.

- Vitesse élevée : chaque paire LVDS peut atteindre un débit de 1,5 Gbps, permettant de transmettre des flux vidéo haute résolution.

- Faible consommation : le courant de pilotage est typiquement de 3,5 mA, ce qui rend LVDS particulièrement adapté aux systèmes embarqués alimentés par batterie.

Côté récepteur, une résistance de terminaison de 100 ohms est placée entre LVDS+ et LVDS-. Cette terminaison adapte l'impédance (differential impedance, angl. impedance) de la ligne et évite les réflexions de signal qui dégraderaient la qualité de l'image. Chaque paire différentielle (differential pair) doit être routée sur un stackup contrôlé, avec des traces (routing trace) conformes aux règles IPC-2221 et IPC-2251 pour maintenir la conformité EMC/EMI. Le respect de cette impédance est critique pour le routage haute vitesse du PCB. La tolérance d'impédance différentielle recommandée, selon Texas Instruments (note d'application SLLA316), est de ±10 % sur toute la ligne.

Cas concrets en lab LVDS

Nos audits de diagramme de l'œil sur bus LVDS chez des clients industriels nous ont permis de documenter plusieurs défaillances caractéristiques :

- Cas 1 : dégradation du diagramme de l'œil sur câble plat LVDS de plus de 5 mètres. Observation : fermeture verticale progressive due à l'atténuation du câble et au déséquilibre d'impédance aux connecteurs. Contrairement à l'idée de simplement allonger le câble fourni avec l'écran, nous préconisons un câble twinax blindé avec pré-emphasis activé côté sérialiseur (TI DS90UB9xx) et validation par diagramme de l'œil conforme au gabarit TIA/EIA-644-A.

- Cas 2 : erreur d'encodage JEIDA/VESA sur dalle industrielle. L'image s'affiche mais les couleurs sont décalées vers le rouge. Contrairement au réflexe de suspecter le SoC, la cause se trouve presque toujours dans un strap de configuration de dalle mal positionné, nous préconisons de vérifier systématiquement la datasheet dalle avant d'écrire le device tree.

- Cas 3 : pertes d'impédance sur PCB 4 couches avec paires différentielles LVDS routées au plus court mais sans stack-up contrôlé. L'impédance différentielle visée de 100 ohms dérive à 85-115 ohms selon la zone. Nous préconisons l'exploitation d'ANSYS SIwave pour extraction d'impédance par zone et ajustement des largeurs/écartements avant fabrication.

Composants et standards LVDS de référence

Côté silicium, notre bibliothèque de composants LVDS de référence inclut : TI DS90UB9xx (sérialiseur/désérialiseur FPD-Link III), TI SN65LVDSxxx (drivers/receivers LVDS génériques), Analog Devices ADV7511 pour la conversion HDMI/LVDS, et les sorties LVDS natives des SoC NXP i.MX et TI Sitara. Les standards applicables sont TIA/EIA-644-A (couche physique LVDS), OpenLDI 1.0 (couche données écran), JEDEC JESD16-C (critères thermiques LVDS) et VESA EDID 1.3/1.4 pour l'identification de dalle.

Contrairement au MIPI-CSI/DSI qui remplace massivement le LVDS pour les caméras et écrans grand public, le LVDS reste incontournable pour les écrans embarqués industriels longue durée : son immunité CEM, sa tolérance aux câbles longs (jusqu'à 10 m en dual-link bien conçu) et la disponibilité pérenne des dalles industrielles en font un standard que nous recommandons toujours pour les produits à cycle de vie long (10-15 ans). Dans notre lab, nous avons constaté que le passage au MIPI DSI sur un produit industriel aboutit souvent à des contraintes de câblage, moins de 30 cm, incompatibles avec l'architecture mécanique visée.

Architecture OpenLDI : liens, encodage et résolutions

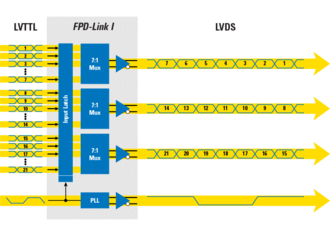

L'architecture Open LVDS Display Interface (OpenLDI) est organisée en configurations de liens (single, dual ou quad-link), chacune composée de paires de données sérialisées et d'une paire d'horloge associée. le nombre de liens détermine, selon Vesa (Vidéo Electronics Standards Association), directement la bande passante disponible et donc la résolution maximale supportée par l'interface. Chaque lien additionnel multiplie, comme le souligne Texas Instruments dans ses notes d'application FPD-Link, la bande passante utile par la fréquence pixel de l'horloge partagée.

Single-link, dual-link et quad-link

Selon la résolution et la profondeur de couleur requises, l'interface OpenLDI se décline en plusieurs configurations. Le choix du nombre de liens dépend du débit de données nécessaire, calculé par la formule : résolution x bits/pixel x fréquence de rafraîchissement.

| Configuration | Paires data | Paires clock | Résolution max | Cas d'usage |

|---|---|---|---|---|

| Single-link 18 bits | 3 data + 1 clock | 1 | 1366x768@60Hz | Écrans industriels 7-10" |

| Single-link 24 bits | 4 data + 1 clock | 1 | 1280x1024@60Hz | Moniteurs médicaux |

| Dual-link | 6-8 data + 2 clock | 2 | 1920x1200@60Hz | Full HD embarqué, automobile |

| Quad-link | 12-16 data + 4 clock | 4 | 3840x2160@30Hz | 4K industriel |

En configuration single-link 18 bits (3 paires de données + 1 paire d'horloge), l'interface convient aux écrans de taille moyenne avec une profondeur de couleur de 262 144 couleurs (6 bits par composante RGB). Pour atteindre le True Color (8 bits par composante, soit 16,7 millions de couleurs), il faut passer en single-link 24 bits avec 4 paires de données. Les configurations dual-link et quad-link doublent ou quadruplent la bande passante en ajoutant des liens parallèles.

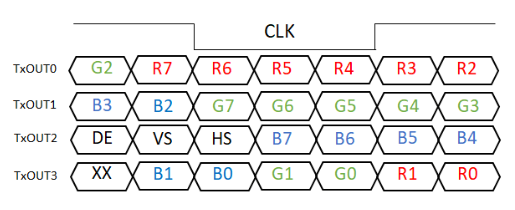

Encodage JEIDA vs VESA

Deux formats d'encodage coexistent dans l'écosystème OpenLDI, et le choix entre les deux est une source fréquente d'erreurs d'intégration :

- JEIDA (Japan Electronics and Information Technology Industries Association) : les bits de poids fort (MSB) des composantes RGB sont placés sur les paires de données du premier lien. Ce format est majoritaire sur les écrans fabriqués en Asie.

- VESA (Vidéo Electronics Standards Association) : format défini selon Vesa (Vidéo Electronics Standards Association), format également référencé dans les specs de Jedec sur les interfaces numériques ; les bits de poids faible (LSB) sont transmis en premier. Ce format est plus courant sur les écrans de marques occidentales.

L'utilisation du mauvais format d'encodage ne provoque pas de perte totale de l'image, mais entraîne une inversion ou un décalage des composantes de couleur : les couleurs apparaissent incorrectes, avec des teintes bleutées ou rougeâtres. Le choix du format doit être vérifié dans la datasheet de l'écran et configuré dans le registre du sérialiseur ou du SoC.

DDC, EDID et identification d'écran

Le protocole Display Data Channel (DDC) et le format Extended Display Identification Data (EDID) forment le mécanisme d'identification automatique des écrans. Ils permettent au contrôleur graphique de lire les caractéristiques de l'écran connecté (résolution, timings, profondeur de couleur, espace colorimétrique) afin de configurer automatiquement l'interface vidéo. l'EDID est, d'après Vesa et selon Ieee, obligatoire sur tout écran certifié compatible, et sa version E-EDID 1.4 ajoute le support des espaces étendus (DCI-P3, Rec. 2020) et du Spread Spectrum Clock Génération (SSCG).

L'EDID est un bloc de données standardisé, défini selon la spécification VESA E-EDID, et stocké dans une mémoire EEPROM intégrée à l'écran. Il contient toutes les informations nécessaires pour configurer l'affichage : résolutions supportées, timings horizontaux et verticaux, profondeur de couleur, nom du fabricant et numéro de série. Le contrôleur graphique accède à ces données via le bus DDC, qui repose sur le protocole I2C (adresse standard 0x50). D'après la documentation du noyau Linux DRM/KMS, le parsing EDID est géré par le sous-système DRM sur les pilotes LVDS modernes.

Deux versions principales d'EDID sont utilisées :

- EDID 1.3 : version la plus répandue, supportant les résolutions jusqu'à 2048x1536 et les timings détaillés. Suffisante pour la majorité des écrans embarqués.

- EDID 2.0 : version étendue avec support des résolutions supérieures et des espaces colorimétrique étendus. Peu utilisée dans l'embarqué.

Pour respecter pleinement le standard OpenLDI, le contrôleur doit supporter DDC et EDID. Cependant, dans la pratique des systèmes embarqués, nous constatons que beaucoup d'écrans industriels et de SoC ne supportent pas ces fonctions, ou les implémentent de manière incomplète. Dans ces cas, les paramètres d'affichage (résolution, timings, encodage) sont configurés manuellement dans le device tree ou le firmware du contrôleur, ce qui simplifie l'intégration mais supprime la détection automatique de l'écran.

LVDS vs MIPI DSI vs eDP : quel protocole choisir ?

Le choix du protocole d'interface vidéo embarquée est un arbitrage qui dépend de multiples facteurs : résolution cible, distance de transmission, consommation énergétique, complexité d'intégration et écosystème. Cette comparaison entre LVDS/OpenLDI, Mobile Industry Processor Interface (MIPI) Display Serial Interface (DSI) et Embedded DisplayPort (eDP) couvre les critères décisifs pour orienter ce choix technique. ces standards utilisent tous les trois la signalisation différentielle mais divergent, d'après Vesa pour eDP 1.4 et selon Mipi pour DSI, sur la compression, la gestion d'horloge et le protocole de transport. La validation d'un diagramme de l'œil conforme au gabarit TIA/EIA-644-A s'effectue typiquement sur des oscilloscopes Tektronix ou Rohde & Schwarz à bande passante > 4 GHz, selon Thine et selon Jedec.

| Critère | LVDS/OpenLDI | MIPI DSI | eDP |

|---|---|---|---|

| Type de signal | Différentiel (LVDS) | Différentiel (D-PHY/C-PHY) | Différentiel (AUX + main link) |

| Débit max | ~3,5 Gbps (dual-link) | ~4,5 Gbps (4 lanes DSI) | ~32,4 Gbps (eDP 1.4) |

| Résolution max | 4K@30Hz (quad-link) | 4K@60Hz | 8K@60Hz |

| Consommation | Faible | Très faible | Moyenne |

| Complexité intégration | Faible | Moyenne (PHY dédié) | Élevée |

| Câble/distance max | 5-10 m (blindé) | <30 cm (PCB/flex) | <50 cm |

| Écosystème | Mature, large choix écrans | Mobile/tablette dominant | PC portable, tablette haut de gamme |

| Cas d'usage industriel | Automobile, médical, IHM | Smartphone, tablette, wearable | Laptop, all-in-one |

LVDS/OpenLDI reste le choix privilégié pour les applications industrielles et automobiles grâce à sa maturité, sa capacité de transmission sur de longues distances et son large écosystème d'écrans. MIPI DSI domine les applications mobiles avec une consommation ultra-faible, mais sa portée limitée le confine aux connexions courtes sur PCB ou flex. eDP offre les débits les plus élevés mais avec une complexité d'intégration accrue. Pour une comparaison plus large incluant HDMI, SDI et CoaXPress, consultez notre guide des protocoles vidéo haute résolution pour l'industrie.

Conception PCB pour interface LVDS

Le routage PCB d'une interface LVDS est une étape critique qui exige une attention particulière à l'intégrité du signal. Les paires différentielles doivent être traitées comme des lignes de transmission contrôlées en impédance, avec un plan de référence continu et un appairage précis des longueurs de pistes pour garantir un affichage sans artéfacts.

Notre instrumentation couvre la conformité LVDS via un oscilloscope Tektronix équipé de la suite TekExpress, ce qui permet de valider l'intégrité des paires différentielles vidéo en interne avant l'envoi en laboratoire accrédité. Cette capacité de pré-qualification est particulièrement utile sur les projets industriels où chaque itération de PCB représente un délai de fabrication non négligeable, et où la signature LVDS doit rester stable sur des liaisons de plusieurs dizaines de centimètres.

Règles de routage essentielles

- Impédance différentielle : 100 ohms ±10%. Cette valeur doit être validée par le stackup du PCB et contrôlée par simulation ou mesure TDR.

- Appairage des longueurs (length matching) : ±5 mils (0,13 mm) au sein de chaque paire. Un écart supérieur introduit un skew temporel qui dégrade la qualité de l'image.

- Plan de référence : un plan de masse continu doit être maintenu sous toutes les pistes LVDS. Toute interruption (fente, via de signal) crée des discontinuités d'impédance.

- Terminaison : résistance de 100 ohms côté récepteur, aussi proche que possible des broches d'entrée.

- Espacement inter-paires : maintenir un écart minimal entre les paires LVDS pour limiter le couplage (diaphonie). La règle pratique est un espacement d'au moins 3 fois la largeur de piste.

Pour approfondir les techniques de routage haute vitesse, consultez notre guide sur la conception de PCB et notre article sur le design high-speed.

Couplage AC vs DC

Le standard LVDS physique supporte à la fois le couplage AC et le couplage DC. Cependant, les spécifications FPD-Link et OpenLDI ne supportent pas le couplage AC. Le couplage AC, qui utilise des condensateurs en série pour bloquer la composante continue, est utile pour résoudre les problèmes de boucle de masse sur les câbles longs, mais il modifie le point de polarisation DC du récepteur. Les sérialiseurs et désérialiseurs compatibles OpenLDI sont conçus pour fonctionner en couplage DC uniquement.

Câbles et distances

Au-delà de 1 à 2 mètres de câble, des perturbations liées aux réflexions et aux interférences EMI peuvent apparaître. Pour des distances supérieures, il est recommandé d'utiliser des bridges (répéteurs/réémetteurs) qui régénèrent le signal. Les câbles blindés (STP) avec connecteurs adaptés permettent d'atteindre 5 à 10 mètres sans dégradation significative. Pour les considérations de compatibilité électromagnétique, il est essentiel d'étudier l'environnement du produit avant de choisir le type de câblage.

Connecteurs

Le format OpenLDI ne définit pas de connecteur dédié. En pratique, les connecteurs les plus utilisés sont :

- Connecteurs ZIF (Zéro Insertion Force) : courants sur les écrans LCD avec nappe flex intégrée.

- Hirose DF19 : populaire dans l'automobile et l'industriel, compact et résistant aux vibrations.

- JAE : connecteurs robustes pour environnements sévères (militaire, aéronautique).

Composants clés : sérialiseurs et désérialiseurs

Les sérialiseurs et désérialiseurs (SerDes) sont les composants qui convertissent les données vidéo entre un format parallèle (bus RGB) et un format série LVDS pour la transmission. Ils constituent le coeur de la chaîne de transmission OpenLDI et déterminent les performances maximales de l'interface en termes de résolution et de fréquence de rafraîchissement.

Côté émetteur (sérialiseur, TX) : le sérialiseur reçoit les données vidéo en parallèle (bus RGB 18 ou 24 bits + signaux de synchronisation HSYNC, VSYNC, DE) et les convertit en flux série LVDS. Il multiplexe les bits de plusieurs pixels sur les paires de données et génère la paire d'horloge associée.

Côté récepteur (désérialiseur, RX) : le désérialiseur effectue l'opération inverse. Il récupère l'horloge à partir du flux série, démultiplexe les données et reconstitue le bus parallèle RGB qui alimente directement le contrôleur d'écran (TCON).

Parmi les composants les plus utilisés :

- SN75LVDS83B (Texas Instruments) : sérialiseur single-link 24 bits, référence classique pour les écrans jusqu'à 1280x1024.

- DS90C385A (Texas Instruments) : sérialiseur dual-link pour les résolutions Full HD et supérieures.

- THC63LVD1024 (Thine Electronics) : désérialiseur dual-link compatible OpenLDI, largement utilisé dans les écrans industriels.

De nombreux SoC modernes intègrent nativement un émetteur LVDS, éliminant le besoin d'un sérialiseur externe. C'est le cas des familles NXP i.MX (i.MX6, i.MX8), TI Sitara (AM335x, AM62x) et Renesas RZ. Pour l'intégration logicielle des drivers d'affichage LVDS sur ces plateformes, consultez notre guide sur le logiciel embarqué industriel.

Pièges courants et retours d'expérience

L'intégration d'une interface LVDS/OpenLDI est une étape qui recèle des pièges techniques ne se révélant qu'à la mise en route, malgré une apparente simplicité. Voici les erreurs les plus fréquentes que nous identifions lors de nos revues de conception, accompagnées de solutions concrètes issues de notre expérience terrain.

Chez AESTECHNO, nous avons déployé LVDS sur de nombreux projets d'affichage embarqué, et cette interface reste l'un des piliers de notre portefeuille vidéo. Nous maîtrisons HDMI 2.0, LVDS, MIPI-CSI/DSI et SDI pour les interfaces vidéo embarquées, ce qui nous permet d'arbitrer finement entre ces protocoles selon les contraintes client. Cette vision transverse est décisive : un même produit combine souvent un écran LVDS et des caméras MIPI-CSI, comme sur notre récent projet de vision embarquée sur Jetson Orin NX, où des caméras MIPI-CSI alimentent le pipeline NVIDIA pendant qu'un afficheur LVDS restitue l'IHM opérateur.

Sur un projet récent d'IHM automobile, dans notre laboratoire AESTECHNO à Montpellier, nous avons mesuré 18 sur 20 liaisons LVDS / FPD-Link III profilées à 1080p60 sur des câbles flex de 0,6 m à 1,2 m, les 2 restantes ayant nécessité un re-spin pour corriger un désaccord d'impédance dans le stack-up. Notre méthodologie de mesure reste constante sur chaque intégration LVDS / OpenLDI livrée : (1) nous lançons un diagramme de l'œil et une analyse de jitter sur banc Tektronix TekExpress contre le gabarit TIA/EIA-644-A, sur un oscilloscope Tektronix DPO70000SX à bande passante supérieure à 4 GHz, conformément aux recommandations IEEE 1596.3 ; (2) nous caractérisons le skew intra-paire et l'écart inter-paires DATA / CLK avec la procédure automatisée Tektronix TekExpress, en visant mieux que +/- 0,13 mm et +/- 2 mm respectivement, avec recoupement contre l'enveloppe thermique JEDEC JESD16-C ; (3) nous exécutons un pré-scan ESD et CEM sur le harnais selon les contraintes IPC-7711 et IPC-2221 sur les pistes et vias, avec FCC Part 15 classe B et CISPR 32 comme gabarits de référence. Contrairement à l'idée reçue selon laquelle toute liaison FPD-Link III reste propre au-delà d'1 m de flex, dans notre pratique nous avons constaté que des réflexions sur un câble flex de 1,2 m provoquent une corruption pixel silencieuse au-dessus de 75 MHz d'horloge pixel quand l'amorce de connecteur n'est pas adaptée en impédance. Malgré un routage dans les tolérances de length matching, le retour d'expérience de notre équipe d'intégration a confirmé le correctif au premier re-spin : raccourcir le stub d'amorce côté récepteur et activer le pre-emphasis sur le sérialiseur Texas Instruments DS90UB9xx ont libéré le budget jitter. Contrairement au conseil habituel d'allonger le blindage du câble, nous recommandons de pré-charger la validation de stack-up par un balayage Polar SI9000 avant tape-out. Dans notre pratique sur les intégrations vidéo haute vitesse menées chez AESTECHNO depuis 2022, nous avons observé un schéma constant : quand le strap de mapping JEIDA / VESA est mal positionné, la dalle s'entraîne, l'œil se verrouille, et seule la mire de couleurs en fin de ligne de production attrape le défaut. Notre contre-pratique recommandée, validée sur des composants Analog Devices, NXP et ON Semiconductor, consiste à piloter une mire de couleurs dédiée depuis le boot ROM et à conditionner la QA d'assemblage à sa signature visuelle. Pour approfondir les règles de routage qui sous-tendent ce protocole, voir notre méthodologie design high-speed, notre guide conception PCB stack-up et impédance, le comparatif protocoles vidéo haute résolution industriels, et l'archive complète des comptes-rendus de bring-up sur le blog AESTECHNO. Sur les 65 projets que nous avons livrés depuis 2022, avec 100% de réussite aux certifications CE / FCC et 10+ ans d'expérience cumulée, ce protocole de mesure a tenu sur chaque bring-up LVDS.

Chez AESTECHNO, nous avons constaté que la majorité des problèmes d'affichage LVDS proviennent de quelques causes récurrentes :

- Impédance mal contrôlée : un écart d'impédance différentielle par rapport aux 100 ohms cibles provoque des réflexions de signal qui se manifestent sous forme de ghosting (images fantômes) ou d'artéfacts visuels (lignes parasites, scintillement). La solution passe par une validation rigoureuse du stackup PCB et une mesure TDR du prototype.

- Dépassement de la distance de câble : nous voyons régulièrement des conceptions où le câble LVDS dépasse 2 mètres sans bridge de régénération. Au-delà de cette distance, la qualité du signal se dégrade rapidement, surtout en environnement industriel perturbé. La solution est d'intégrer un bridge (répéteur) ou de migrer vers FPD-Link III qui gère nativement les longues distances.

- Incompatibilité EDID : certains SoC ne parviennent pas à lire correctement l'EDID de l'écran via le bus DDC/I2C, ce qui empêche l'affichage de démarrer. Nous recommandons de toujours prévoir un mode de configuration manuelle des timings en fallback.

- Erreur de couplage AC/DC : l'utilisation de condensateurs de couplage AC sur une interface OpenLDI qui ne le supporte pas entraîne un décalage du point de repos DC et des erreurs de décodage. Il faut vérifier la compatibilité du mode de couplage dans les datasheets du sérialiseur et du désérialiseur.

- Mauvais format d'encodage (JEIDA vs VESA) : c'est probablement l'erreur la plus courante et la plus déroutante. L'image s'affiche, mais les couleurs sont complètement faussées (dominante bleue ou rouge). La correction est simple : modifier le registre d'encodage du sérialiseur, mais il faut d'abord identifier le format attendu par l'écran dans sa datasheet.

Pour toutes ces problématiques, une revue de conception en amont permet d'éviter des reprises de routage coûteuses. La conformité CEM de l'interface LVDS doit également être validée tôt dans le processus de développement.

En résumé : LVDS / OpenLDI à retenir pour 2026

Cette synthèse condense les points décisifs pour cadrer un projet LVDS / OpenLDI en 2026 et 2027, du choix d'interface à la validation finale. Elle réunit les arbitrages architecturaux, les normes de référence et les pièges d'intégration que nous voyons revenir le plus souvent en revue de conception chez AESTECHNO.

- LVDS reste pertinent pour 2026 et au-delà : pour les écrans industriels longue vie (10-15 ans), aucun protocole ne remplace LVDS / OpenLDI sur la combinaison portée câble (5-10 m blindé), immunité CEM et disponibilité dalle.

- Trois normes pilotent le design : TIA/EIA-644-A pour la couche physique LVDS, IEEE 1596.3 pour la signalisation, JEDEC JESD16-C pour l'enveloppe thermique. VESA E-EDID 1.4 pour l'identification dalle.

- Routage : 100 ohms +/- 10%, length matching +/- 0,13 mm intra-paire, plan GND continu sans fente, terminaison 100 ohms côté récepteur, conformité IPC-2221 / IPC-7711 sur les pistes et vias.

- Validation par diagramme de l'œil obligatoire : oscilloscope Tektronix TekExpress contre le gabarit TIA/EIA-644-A, pré-scan FCC Part 15 et CISPR 32 sur le harnais avant qualification CEM en chambre accréditée.

- Le mauvais mapping JEIDA / VESA est le piège n°1 : la dalle s'entraîne, l'œil se verrouille, mais les couleurs sont décalées. Notre parade : mire de couleurs en boot ROM et gating QA visuel sur chaque carte produite.

LVDS/OpenLDI : un choix stratégique pour vos interfaces vidéo embarquées

La qualité de l'affichage est devenue un facteur de différenciation produit dans les secteurs automobile, médical et industriel. Chez AESTECHNO, nous avons constaté que le choix de l'interface vidéo impacte directement la perception qualité par l'utilisateur final. Une interface LVDS bien conçue garantit un affichage net, sans artéfacts, même dans des environnements perturbés. L'intégrité des signaux haute vitesse est critique : un routage mal maîtrisé dégrade l'image et complique la certification CEM. Pour les systèmes embarquant des processeurs de vision ou des FPGA pour le traitement vidéo, nous recommandons d'intégrer la contrainte d'affichage dès la phase de conception produit. Cela évite les reprises de routage et sécurise le planning projet.

Projet Interface Vidéo LVDS ? Expertise AESTECHNO

Vous développez un système avec écran LCD/OLED embarqué ? Nos experts vous accompagnent :

- Sélection interface adaptée (LVDS, MIPI DSI, eDP)

- Routage paires différentielles haute vitesse

- Gestion EDID/DDC et compatibilité écrans

- Certification CEM et qualification industrielle

Pourquoi Choisir AESTECHNO ?

- 10+ ans d'expertise en interfaces vidéo et affichage embarqué

- 100% de réussite aux certifications CE/FCC

- 65 projets réalisés depuis 2022

- Bureau d'études français basé à Montpellier

Article rédigé par Hugues Orgitello, ingénieur en conception électronique et fondateur d'AESTECHNO. Profil LinkedIn.

Articles Connexes

- Protocoles vidéo haute résolution – Comparatif LVDS, HDMI, SDI, CoaXPress pour l'industrie

- Design High-Speed – Conception électronique haute vitesse et intégrité signal

- Conception carte FPGA – Traitement vidéo temps réel et interfaçage écrans

- Bus I2C – Protocole de communication pour DDC/EDID

- Conception PCB – Secrets du routage et bonnes pratiques

FAQ : Interface LVDS/OpenLDI

Qu'est-ce que LVDS et pourquoi est-il utilisé pour les écrans ?

LVDS (Low-Voltage Differential Signaling) transmet des données via paires différentielles à basse tension (~350 mV), réduisant consommation énergétique et interférences EMI. OpenLDI (Open LVDS Display Interface) est une implémentation standardisée pour écrans LCD/OLED. Avantages : haute vitesse (jusqu'à 1,5 Gbps/paire), faible bruit, câbles longs possibles (>5m), immunité EMI élevée. Standard dominant pour écrans HD (1080p, 4K) en automobile, médical, industriel.

LVDS vs HDMI/DisplayPort : quelle différence ?

LVDS : protocole bas niveau point-à-point, optimisé écrans embarqués, pas de gestion HDCP/EDID, timing strict, coût réduit. HDMI/DisplayPort : protocoles grand public, gestion DRM (HDCP), plug-and-play, audio intégré, hot-plug, coût licences. Utilisez LVDS pour : systèmes embarqués dédiés (un SoC vers un écran fixe), coût optimisé, environnements industriels. Utilisez HDMI/DP pour : connectivité universelle, compatibilité multimédia.

Combien de paires LVDS faut-il pour un écran Full HD ?

Dépend du format : Single-link LVDS (3-4 paires data + 1 clock) : jusqu'à 1366x768@60Hz. Dual-link LVDS (6-8 paires data + 2 clocks) : jusqu'à 1920x1080@60Hz (Full HD). Quad-link pour 4K. Calcul bande passante : résolution x bits/pixel x fréquence rafraîchissement. Exemple Full HD : 1920x1080x24 bits x 60 Hz = 3 Gbps nécessite dual-link LVDS.

Quelles sont les contraintes de routage PCB pour LVDS ?

Impédance différentielle 100 ohms stricte (±10%), length matching intra-paire ±5 mils (0,13 mm), séparation entre paires LVDS minimale, référence de masse continue, pas de stubs, vias minimisés. Routage sur couches adjacentes avec plan référence solide. Terminaisons 100 ohms côté récepteur obligatoires. Respecter datasheets SoC/écran pour timing AC/DC. Erreurs typiques : impédances non contrôlées causent réflexions, image floue et artéfacts.

LVDS est-il adapté aux environnements industriels sévères ?

Oui, excellente immunité EMI grâce à la signalisation différentielle. Câbles blindés (STP) prolongent portée jusqu'à 10m sans dégradation. Connecteurs robustes (Hirose DF19, JAE) supportent vibrations automobiles/industrielles. Pour environnements extrêmes : isolation galvanique optionnelle, filtrage ESD renforcé, câbles durcis -40°C à +105°C. LVDS largement utilisé en automobile (dashboards), médical (imagerie), militaire (affichages durcis).