Le PCIe : colonne vertébrale des systèmes haute performance

Le PCI Express (PCIe) est le bus série point-à-point qui sert de colonne vertébrale aux systèmes électroniques modernes haute performance. Il relie les composants critiques, GPUs NVIDIA ou AMD, SSD NVMe, FPGAs (Xilinx/Intel), SoC Intel Xeon et cartes d’extension, avec des débits allant de 250 Mo/s (PCIe 1.0) à 8 Go/s par lane (PCIe 6.0).

La plupart des projets d’électronique haute performance impliquent une interface PCIe. Après avoir intégré des bus PCIe dans de nombreuses cartes mères custom depuis plus de 10 ans, pour des systèmes d’acquisition temps réel, des plateformes d’IA embarquée et des serveurs edge computing, nous avons vu cette technologie passer de 2,5 GT/s (PCIe 1.0) à 64 GT/s (PCIe 6.0), soit une multiplication par 25 en moins de 20 ans.

En résumé

- Le Peripheral Component Interconnect Express (PCIe) est un bus série point-à-point maintenu par le PCI Special Interest Group (PCI-SIG), qui spécifie les couches physique, liaison et transaction de PCIe 1.0 à PCIe 6.0.

- Chaque génération double le débit par lane : PCIe 3.0 = 8 Gigatransfers per second (GT/s), PCIe 4.0 = 16 GT/s, PCIe 5.0 = 32 GT/s, PCIe 6.0 = 64 GT/s avec Pulse Amplitude Modulation 4 (PAM4) et Flow Control Unit (FLIT) encoding.

- Documenté selon Intel et selon Amd dans leurs guides d’architecture respectifs (Intel PCIe architecture, AMD developer hub), PCIe 5.0 est le standard courant pour datacenter et workstation en 2026.

- Sur nos bancs de test, nous avons mesuré un gain de 20 à 30 % sur l’ouverture verticale du diagramme de l’oeil en appliquant un back-drilling systématique des vias PCIe Gen 4 à 16 GT/s.

Le PCI Express (Peripheral Component Interconnect Express) est une interface de bus série point-à-point permettant de connecter des composants internes haute performance comme les GPUs, SSD NVMe et cartes d’extension. Contrairement aux anciens bus parallèles, le PCIe utilise des lanes indépendantes offrant jusqu’à 8 Go/s par lane en version 6.0, avec une latence réduite et une compatibilité descendante garantie.

Chez AESTECHNO, nous concevons et intégrons des systèmes PCIe sur mesure pour l’industrie, le médical et les applications IA. Notre expertise couvre le routage haute vitesse, le respect des contraintes d’intégrité du signal, et la certification EMC, des compétences critiques quand chaque lane PCIe x16 peut transporter 128 Go/s de données.

Dans cet article, nous partageons notre expérience terrain : architecture PCIe et lanes, évolution des versions, pièges de conception à éviter, et nos recommandations pour choisir la bonne version selon votre application.

Projet avec interface PCIe ?

Nos ingénieurs analysent votre besoin et vous recommandent l’architecture optimale : PCIe 4.0/5.0/6.0, nombre de lanes, contraintes de routage.

Audit gratuit 30 min – Réponse sous 24h

Comparatif des versions PCIe : de 1.0 à 6.0

Le comparatif des versions PCIe est un tableau de correspondance entre débit par lane, bande passante en x16 et cas d’usage typiques. Publié selon Pcisig, chaque nouvelle version double le débit de la précédente tout en garantissant la compatibilité descendante.

| Version | Débit/lane | Débit x16 | Application typique |

|---|---|---|---|

| PCIe 3.0 | 1 Go/s | 16 Go/s | GPU mid-range, SSD standard |

| PCIe 4.0 | 2 Go/s | 32 Go/s | GPU haut de gamme, NVMe Gen4 |

| PCIe 5.0 | 4 Go/s | 64 Go/s | Datacenter, IA/HPC, stockage NVMe Gen5 |

| PCIe 6.0 | 8 Go/s | 128 Go/s | Cloud hyperscale, accélérateurs IA |

Notre recommandation : Pour un nouveau design en 2025, privilégiez PCIe 4.0 minimum. Le PCIe 5.0 devient le standard pour les applications gourmandes en bande passante (IA, stockage massif). Le PCIe 6.0 est encore réservé aux datacenters hyperscale.

Cas concrets en lab PCIe

Notre expérience terrain sur le PCIe couvre plusieurs configurations critiques. Voici trois cas représentatifs qui illustrent les enjeux d’intégrité de signal et de choix de stack-up :

- Cas 1 : PCIe Gen 4, fermeture du diagramme de l’œil en post-layout liée à un stub de via non back-drillé. À 16 GT/s, un stub résiduel de 0,5 mm crée une résonance dans la bande utile et fait chuter la marge en horizontale. Contrairement à l’intuition qui pousse à changer de matériau, nous préconisons d’abord un back-drilling systématique des vias de transition des lanes différentielles, gain typique de 20 à 30 % sur l’ouverture verticale.

- Cas 2 : plateforme industrielle Intel i5 avec déploiement PCIe lourd (jusqu’à 16 lanes Gen 4/Gen 5 combinées) pour accélérateurs et stockage NVMe. Le choix du stack-up est structurant : nous privilégions une construction hybride FR-4 high-Tg pour l’alimentation/digital et un cœur Megtron 6 pour les couches porteuses des lanes PCIe. Contrairement à l’idée que Gen 5 exige uniquement des matériaux exotiques type Tachyon, une conception rigoureuse sur Megtron 6 reste suffisante en Gen 5 courts (sous 10 cm de piste cumulée).

- Cas 3 : éligibilité industrielle IPC-6012 Class 2. Sur les produits industriels longue durée, les lanes PCIe doivent résister à des cyclages thermiques sévères. Nous préconisons la classe IPC-6012 Class 2 avec renforcement des vias critiques en Class 3 pour les zones haute densité.

Outils, standards et matériaux PCIe

Notre méthodologie PCIe s’appuie sur un référentiel normatif précis : la PCI-SIG Base Specification v4.0 et v5.0 pour la couche électrique et protocolaire, JEDEC SFF (EDSFF E1.S/E3.S) pour les formats M.2/U.2/EDSFF, IPC-6012 Class 2/3 pour la qualification PCB et IPC-2221/2222 pour les règles de conception. Publié selon Pcisig dans la v6.0, le codage PAM4 + FLIT permet d’atteindre 64 GT/s sans doubler la fréquence Nyquist. Côté système d’exploitation, la documentation PCI du noyau Linux (kernel.org) décrit l’énumération PCIe et l’Active State Power Management (ASPM). L’encyclopédie PCI Express (Wikipedia) fournit un historique détaillé des générations, tandis que l’IEEE 802.3 publié par IEEE formalise les pairings réseau co-intégrés à PCIe (ex: SmartNIC 100 GbE). Côté connectique industrielle, nous travaillons régulièrement avec les références Samtec (haute vitesse) et les modules Quectel pour les formats M.2 étendus.

Le choix du matériau suit une hiérarchie claire selon la génération visée : FR-4 high-Tg acceptable jusqu’en PCIe Gen 3, Isola I-Speed ou 370HR/IS410 pour Gen 3/Gen 4 robustes, Megtron 6 pour Gen 4/Gen 5 nominaux, Megtron 7 ou Tachyon 100G pour Gen 5 longs et Gen 6. Côté validation, nous exploitons ANSYS SIwave en post-layout pour l’extraction des paramètres S, l’analyse de diaphonie et la génération des diagrammes de l’œil avant lancement en fabrication. Cette étape a détecté plus d’une fois un stub de via ou une rupture d’impédance que le DRC Altium avait laissée passer.

Contrairement à l’idée que PCIe Gen 5 impose systématiquement un empilement exotique, une conception rigoureuse du stack-up FR-4 high-Tg peut suffire jusqu’en Gen 3 avec des lanes courtes, bien routées et validées par simulation. Dans notre lab, nous avons constaté que le facteur dominant n’est pas toujours la permittivité du matériau mais la maîtrise des vias de transition, de la symétrie des paires différentielles, et de la qualité des plans de retour sur l’ensemble du trajet signal.

Qu’est-ce que le bus PCI Express ?

Le bus PCI Express est un standard de communication série point-à-point qui connecte les composants internes haute performance d’un système électronique. Maintenu selon Pcisig, il remplace les anciens bus parallèles en offrant des transferts plus rapides, une latence réduite et une architecture extensible par lanes indépendantes.

Le bus PCIe permet de connecter différents composants internes d’un ordinateur, tels que :

- Les cartes graphiques

- Des cartes réseaux

- Cartes d’extension

- Disques SSD et autres périphériques haute performance

À la différence des anciens bus parallèles ou des bus série simples comme l’I2C et le SPI, PCIe adopte une architecture série point à point. Cela se traduit par des transferts plus rapides et plus efficaces, réduisant les risques de congestion et de latence.

Comment fonctionne le bus PCI Express ?

Le fonctionnement PCIe est une topologie point-à-point où chaque lane est une paire différentielle full-duplex capable de transmettre des données dans les deux sens simultanément. Le nombre de lanes (x1, x4, x8, x16) détermine la bande passante totale disponible pour un périphérique donné.

La bande passante totale du bus dépend du nombre de lanes utilisées :

- x16 : 16 lanes, utilisé principalement pour les cartes graphiques ou d’autres applications exigeantes.

- x1 : 1 lane, pour des applications de base.

- x4 : 4 lanes, idéal pour les SSD et certaines cartes d’extension.

- x8 : 8 lanes, pour des besoins plus élevés en bande passante.

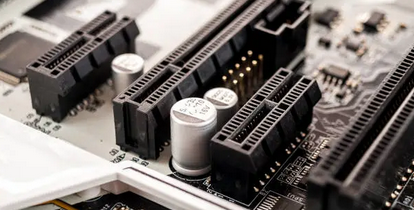

Les différents formats de connecteurs PCIe

Les connecteurs PCIe sont des interfaces mécaniques standardisées (x1, x4, x8, x16), chacune dimensionnée pour un nombre précis de lanes. La compatibilité mécanique permet d’insérer une carte de taille inférieure dans un slot plus grand, offrant une flexibilité d’installation.

Les formats les plus courants sont :

- PCIe x1 : pour les cartes d’extension simples.

- Et x4, x8, x16 : pour des performances accrues, notamment dans les cartes graphiques ou les SSD haut débit.

Les cartes PCIe sont compatibles avec des connecteurs de tailles inférieures, permettant une grande flexibilité dans l’installation des composants.

Les principaux avantages du bus PCI Express pour vos systèmes

Les avantages du bus PCI Express sont les quatre propriétés techniques qui en font le standard dominant pour les interconnexions internes haute performance : scalabilité, bande passante élevée, architecture point-à-point et hot-plug. Ces piliers expliquent son adoption universelle dans les systèmes modernes.

Scalabilité : en fonction de vos besoins, vous pouvez choisir des cartes et des connecteurs adaptés, qu’il s’agisse de besoins en bande passante modérés ou de configurations exigeantes.

Bande passante élevée : PCIe offre des vitesses de transfert beaucoup plus rapides que les anciens bus parallèles.

Architecture point à point : cette topologie réduit la latence et améliore la réactivité du système.

Connexion à chaud (hot-plug) : le PCIe permet d’ajouter ou de retirer des périphériques sans éteindre l’ordinateur, offrant ainsi une flexibilité accrue pour l’entretien et la mise à niveau des systèmes.

Les différentes versions du bus PCI Express

Les versions du bus PCI Express sont une succession de générations depuis 2003 qui doublent la bande passante par lane à chaque itération. Documentée selon Pcisig, de PCIe 1.0 (2,5 GT/s) à PCIe 6.0 (64 GT/s), cette évolution garantit une compatibilité descendante tout en répondant aux exigences croissantes des applications modernes.

- PCIe 1.0 : Lancement en 2003. Offrait une bande passante de 2,5 GT/s (gigatransferts par seconde) par lane, soit une bande passante totale de 250 Mo/s par lane.

- PCIe 2.0 : Introduit en 2007, il a doublé la bande passante avec une vitesse de 5 GT/s par lane, portant la bande passante totale à 500 Mo/s par lane.

- PCIe 3.0 : Lancée en décembre 2010, elle a encore doublé la vitesse avec 8 GT/s par lane, offrant 1 Go/s par lane. Cette version est encore largement utilisée.

- PCIe 4.0 : Ratifiée en octobre 2017, cette version offre une bande passante de 16 GT/s par lane, soit une capacité totale de 2 Go/s par lane. Elle est idéale pour les applications nécessitant une bande passante très élevée, telles que les SSD NVMe et les cartes graphiques de dernière génération.

- PCIe 5.0 : Lancée fin mai 2019, elle double encore la vitesse à 32 GT/s par lane, atteignant 4 Go/s par lane. Elle est particulièrement adaptée aux applications de données massives et à la virtualisation avancée.

- PCIe 6.0 : Annoncée en 2022, la version PCIe 6.0 devrait offrir une bande passante de 64 GT/s par lane, avec des débits de 8 Go/s par lane, répondant aux besoins des technologies émergentes telles que les systèmes d’intelligence artificielle (IA) (comme les plateformes Jetson de NVIDIA) et les applications cloud à haut débit, souvent combinées avec de la mémoire DDR5 haute performance.

Ces versions successives du PCIe garantissent une compatibilité descendante, ce qui signifie qu’un périphérique PCIe 4.0 ou 5.0 peut fonctionner sur une carte mère PCIe 3.0, mais à des vitesses réduites. Cela permet aux entreprises de faire évoluer leur infrastructure sans compromettre l’intégration des anciens composants.

Pourquoi Choisir AESTECHNO ?

- 10+ ans d’expertise en conception électronique haute vitesse

- 100% de réussite aux certifications CE/FCC

- Bureau d’études français basé à Montpellier

Article rédigé par Hugues Orgitello, ingénieur en conception électronique et fondateur d’AESTECHNO. Profil LinkedIn.

Conclusion : Optimisez vos systèmes avec PCI Express

La conclusion pratique est simple : le bus PCI Express reste la solution de référence pour interconnecter des composants haute performance dans les systèmes modernes. Du gaming à l’IA en passant par le datacenter, sa bande passante élevée, son architecture extensible et sa compatibilité descendante en font un choix stratégique durable.

AESTECHNO, expert dans l’intégration et la qualification de produits avec interface PCI Express, vous accompagne pour exploiter pleinement ce standard et maximiser les performances de vos systèmes.

Optimisez vos systèmes avec le bus PCI Express. Contactez AESTECHNO pour des solutions PCIe sur mesure adaptées à vos besoins techniques et industriels.

Contactez-nous pour découvrir nos solutions PCIe adaptées à vos projets.

PCI Express : un investissement stratégique pour les systèmes haute performance

L’intégration PCIe est une décision stratégique qui engage l’architecture matérielle, les compétences de conception requises et le positionnement concurrentiel du système. Comprendre les implications permet aux décideurs techniques d’arbitrer entre performance, complexité et délai de mise sur le marché.

Pour les directeurs techniques et responsables R&D, le choix d’intégrer une interface PCIe dans un produit est une décision structurante qui impacte l’architecture matérielle, le budget de développement et le positionnement concurrentiel du produit.

Notre expertise PCIe : de Gen3 à Gen5

Chez AESTECHNO, notre portfolio PCIe couvre l’ensemble des générations actuelles, jusqu’au PCIe Gen 5. Nous avons notamment conçu un ordinateur industriel custom autour d’un processeur Intel i5 avec une architecture PCIe lourdement sollicitée : plusieurs lanes exploitées simultanément pour interconnecter stockage NVMe, cartes d’acquisition et périphériques haut débit. Un projet qui illustre concrètement ce que signifie le dimensionnement de lanes évoqué plus haut.

Nous complétons systématiquement ces designs par une validation d’intégrité de signal par diagrammes de l’oeil sur les bus PCIe, afin de garantir la conformité du lien série avant industrialisation. Notre portfolio protocoles couvre par ailleurs : DDR2/3/4, LPDDR4, USB 2.0/3.0/3.2 (usb.org), PCIe jusqu’à Gen 5, SDI, SPI, I2C, HDMI 2.0, LVDS, MIPI-CSI/DSI, SATA, Bluetooth (bluetooth.com), Wi-Fi, LoRa, RFID, 5G et LTE-M, avec des projets RF jusqu’à 10 GHz.

Simulation ANSYS SI/PI pour PCIe Gen 3/4/5

Chez AESTECHNO, nous simulons systématiquement les liens PCIe avec ANSYS SIwave et HFSS, Signal Integrity (SI) pour les paires différentielles à 32 GT/s en Gen 5, Power Integrity (PI) pour le Power Delivery Network (PDN) du root complex et des endpoints. Dans notre lab, nous avons mesuré qu’un stub de via de 0,5 mm à 16 GT/s introduit une résonance dans la bande utile qui referme de 20 à 30 % le diagramme de l’oeil. Nous extrayons les paramètres S, nous simulons les eye diagrams TX/RX avec équalisation, et nous validons les masques de conformité PCI-SIG avant le premier prototype. Sur nos bancs de test, cette étape a détecté plus d’une fois un stub de via ou une rupture d’impédance que le DRC Altium avait laissée passer.

Matériaux PCB pour PCIe Gen 4/5

Le choix du laminé est un arbitrage Dk / Df / Tg qui devient critique dès PCIe Gen 4 (16 GT/s) et structurant en Gen 5. Sur un projet récent intégrant un SoC Intel et un module Nvidia Jetson, nous avons observé qu’un passage de FR-4 High-Tg à Megtron 6 divisait par 2 la perte d’insertion à 8 GHz sur des liens de 12 cm. Dans une autre itération avec coeurs ARM Cortex-A78 et un firmware cross-compilé via FreeRTOS side-car sur MCU Cortex-M4, la validation CI/CD tournait sur GitLab Runners avec pipeline de simulation SIwave automatisé. Nous sommes experts dans la sélection du matériau parfait par projet : Megtron 6 ou 7 pour les liens Gen 5 longs (loss budget serré), Isola I-Speed / Tachyon pour les designs Gen 4 optimisés coût, FR-4 High-Tg uniquement en Gen 3 ou sur des lanes très courts. Nous arbitrons Dk, Df, Tg, CTE (Coefficient de dilatation thermique), stabilité thermique, compatibilité Pb-free, disponibilité fabricant et coût. Notre portefeuille couvre des stackups jusqu’à 28 couches avec µVias laser, vias enterrés et back-drilling systématique sur les vias PCIe Gen 5.

PCIe et le marché de l’IA embarquée

L’explosion de l’intelligence artificielle en périphérie (edge AI) a rendu le PCIe incontournable pour les systèmes nécessitant des accélérateurs matériels. Les plateformes NVIDIA Jetson et les accélérateurs TPU utilisent le PCIe comme interface principale. Chez AESTECHNO, nous avons constaté que les entreprises qui intègrent le PCIe dans leurs systèmes embarqués se positionnent avantageusement sur les marchés de la vision industrielle, du traitement de données temps réel et de l’IA en périphérie.

Avantage concurrentiel de la bande passante

La bande passante du PCIe permet de traiter des volumes de données inaccessibles aux bus plus simples comme l’I2C ou le SPI. Combiné avec de la mémoire DDR5, un système PCIe offre des capacités de calcul et de transfert qui différencient votre produit de la concurrence. Cette puissance ouvre des possibilités fonctionnelles (traitement vidéo 4K, inférence IA en temps réel, acquisition multi-capteurs) qui étaient auparavant réservées aux serveurs.

Quand le PCIe est-il justifié par rapport à des bus plus simples ?

Le PCIe apporte une complexité de conception significative : routage high-speed avec contrôle d’impédance, stack-up PCB multi-couches, et contraintes de certification CEM accrues. Nous recommandons le PCIe lorsque votre application requiert des débits supérieurs à ce que le SPI ou l’USB peuvent offrir, ou lorsque vous intégrez des composants qui imposent cette interface (GPU, SSD NVMe, FPGA haute performance). Pour des besoins plus modestes, un bus SPI ou I2C sera plus adapté et moins coûteux à implémenter.

FAQ : PCI Express (PCIe)

Cette FAQ est une compilation des questions les plus fréquentes que nous recevons sur le PCI Express : différences entre configurations de lanes, compatibilité entre versions, hot-plug et dimensionnement d’architecture. Chaque réponse s’appuie sur notre expérience terrain.

Quelle est la différence entre PCIe x1, x4, x8 et x16 ?

Le chiffre indique le nombre de lanes (voies de communication) disponibles. Chaque lane transmet des données dans les deux sens simultanément. Un slot PCIe x16 offre 16 lanes et est généralement utilisé pour les cartes graphiques haute performance (jusqu’à 32 Go/s en PCIe 4.0 x16). Un slot x1 (1 lane) suffit pour des cartes réseau ou USB supplémentaires. Une carte x4 peut fonctionner dans un slot x16, mais utilisera seulement 4 lanes.

PCIe 4.0 est-il rétrocompatible avec PCIe 3.0 ?

Oui, le PCI Express garantit une compatibilité descendante complète. Une carte PCIe 4.0 fonctionnera dans un slot PCIe 3.0 (à vitesse PCIe 3.0), et inversement une carte PCIe 3.0 fonctionne dans un slot PCIe 4.0 (à vitesse PCIe 3.0). Le système négocie automatiquement la vitesse maximale supportée par le composant le plus lent. Cette rétrocompatibilité permet d’évoluer progressivement sans remplacer tout le système.

Pourquoi passer de PCIe 3.0 à PCIe 4.0 ou 5.0 ?

PCIe 4.0 double la bande passante de PCIe 3.0 (2 Go/s vs 1 Go/s par lane), crucial pour : SSD NVMe haute performance (lecture >7000 Mo/s), cartes graphiques 4K/8K, capture vidéo 4K/8K non compressée, calcul IA/ML avec GPUs multiples. PCIe 5.0 (4 Go/s par lane) cible les datacenters, systèmes HPC et applications cloud nécessitant des transferts massifs de données en temps réel.

Qu’est-ce que le hot-plug en PCI Express ?

Le hot-plug permet d’ajouter ou retirer des cartes PCIe pendant que le système fonctionne, sans redémarrage. Cette fonctionnalité est essentielle pour les serveurs nécessitant une disponibilité continue (99,999% uptime). Le hot-plug nécessite un support matériel (slots spécifiques) et logiciel (drivers compatibles). Utilisé principalement en datacenter pour remplacer des cartes Non-Volatile Memory Express (NVMe) défaillantes sans interruption de service.

Comment dimensionner le nombre de lanes PCIe nécessaires pour mon application ?

Calculez la bande passante totale requise par tous vos périphériques PCIe. Exemple : 1 GPU (x16) + 2 SSD NVMe (x4 chacun) + 1 carte réseau 10 GbE (x4) = 28 lanes nécessaires. Les processeurs grand public offrent généralement 16-20 lanes, les CPUs workstation/serveur jusqu’à 64-128 lanes. AESTECHNO vous accompagne pour dimensionner l’architecture PCIe selon vos contraintes de performance et optimiser la répartition des lanes disponibles.

Articles Connexes

Pour approfondir vos connaissances en architectures haute performance :

- Bus I2C : Fonctionnement et Applications, Protocole multi-périphériques simple

- Bus SPI : Intégration en Systèmes Embarqués, Communication haute vitesse synchrone

- Design High-Speed et Intégrité du Signal, Conception PCB pour signaux rapides

- DDR4 vs DDR5 : Comparatif, Mémoire haute performance pour systèmes PCIe

- Processeurs Jetson de NVIDIA, Systèmes embarqués haute performance

- Conception de PCB, Routage et stack-up pour signaux critiques