19 min de lecture Hugues Orgitello

Intégrer le bus SPI dans vos systèmes embarqués

Guide SPI (Serial Peripheral Interface) : applications IoT, capteurs, mémoires Flash, écrans. Haute vitesse full-duplex, gestion CEM, optimisation embarquée.

Le bus SPI, Serial Peripheral Interface (SPI), est un protocole de communication série synchrone à quatre fils incontournable en électronique embarquée. Originellement défini par Motorola (aujourd'hui NXP / Analog Devices) dans les années 1980, le SPI atteint couramment 50 Mbit/s sur MCU modernes et monte en QSPI (Quad SPI) jusqu'à 133 MHz sur les flash NOR conformes au standard JEDEC.

Ce protocole, selon Motorola qui l'a inventé, devait offrir un lien synchrone simple entre microcontrôleur et périphériques, sans surcoût logiciel. D'après Analog Devices, le SPI reste la couche physique privilégiée pour convertisseurs ADC/DAC haute vitesse et capteurs industriels comme l'IIS3DWB. Nous optimisons le bus SPI dans nos projets industriels, IoT et médicaux, du routage PCB contrôlé en impédance à la validation en chambre CEM.

À quoi sert le bus SPI ? Exemples d'applications concrètes

Le bus SPI est un protocole série synchrone conçu pour l'échange de données haute vitesse entre un microcontrôleur maître et un ou plusieurs périphériques esclaves. Il repose sur quatre lignes (MOSI, MISO, SCK, CS) et fonctionne en full-duplex, ce qui le rend particulièrement adapté aux applications embarquées exigeantes en bande passante.

Le SPI est utilisé pour connecter une grande variété de composants à des microcontrôleurs ou des processeurs :

- Capteurs : accéléromètres, gyroscopes, capteurs de température ou de pression.

- Modules de communication : Wi-Fi, Bluetooth, Zigbee pour l'IoT ou la connectivité industrielle.

- Mémoire : Flash, EEPROM, cartes SD pour l'enregistrement ou le traitement de données.

- Affichages : écrans LCD, OLED, TFT pour l'interface homme-machine.

Dans chacun de ces cas, le SPI garantit un transfert de données rapide, fiable et synchrone.

Pourquoi le SPI est-il un protocole stratégique ?

Le bus SPI est un protocole stratégique par sa combinaison de vitesse élevée, de simplicité matérielle et de communication full-duplex. Contrairement à l'I2C qui partage deux fils entre tous les périphériques, le SPI dédie une ligne de sélection par composant, ce qui élimine les conflits d'adressage et permet des débits nettement supérieurs dans les systèmes embarqués modernes.

- Haute vitesse : idéal pour les applications temps réel, avec des performances bien supérieures à celles du bus UART.

- Communication bidirectionnelle simultanée (duplex intégral).

- Simplicité matérielle : peu de lignes, pas de pile logicielle complexe.

- Compatibilité étendue : protocole non breveté et largement répandu, supporté sur toutes les plateformes majeures (STM32, Microchip, NXP, etc.).

SPI vs I2C vs UART : comparaison des protocoles

Le choix entre SPI, I2C et UART est une décision d'architecture qui dépend du débit requis, du nombre de périphériques, du budget en broches et de la complexité du routage PCB. Ce tableau comparatif synthétise les différences clés entre ces trois protocoles de communication série pour orienter la sélection selon votre architecture système.

| Critère | SPI | I2C | UART |

|---|---|---|---|

| Débit max | 50+ Mbit/s | 3,4 Mbit/s | ~1 Mbit/s |

| Nombre de fils | 4 (MOSI, MISO, SCK, CS) | 2 (SDA, SCL) | 2 (TX, RX) |

| Full-duplex | Oui | Non (half-duplex) | Oui |

| Adressage | Par ligne CS (1 par device) | Par adresse (7/10 bits) | Aucun (point-à-point) |

| Cas d'usage typique | Flash, ADC rapides, écrans TFT | Capteurs, EEPROM, RTC | Debug, GPS, Bluetooth (HCI) |

Dans notre pratique, nous combinons fréquemment ces trois protocoles au sein d'un même système embarqué : le SPI pour les périphériques gourmands en bande passante (mémoire Flash, écrans), l'I²C pour les capteurs à faible débit, et l'UART pour le debug et la communication avec des modules externes. Sur MCU STM32 ou ESP32, les drivers SPI sont directement exposés par les stacks Zephyr, FreeRTOS et les HAL propriétaires. Pour les produits NB-IoT ou LoRaWAN, les modems Sigfox, les liens CAN-FD (ISO 11898) ou Modbus RS-485 cohabitent fréquemment avec un bus SPI interne vers la flash de configuration. À l'inverse de l'I²C et de l'I3C, qui multiplexent l'adressage sur deux fils partagés, le SPI conserve une horloge dédiée par maître, ce qui simplifie la coexistence avec un transport CANopen ou J1939 sur la même carte.

Les défis de l'intégration du bus SPI

L'intégration du bus SPI consiste à gérer la cohabitation de périphériques hétérogènes, maîtriser le routage PCB à haute fréquence et garantir la conformité CEM (IEC 61000-4-x) du produit final. Chaque défi mal anticipé peut entraîner des dysfonctionnements intermittents difficiles à diagnostiquer.

- Gestion des vitesses de transmission : Les différents périphériques peuvent avoir des vitesses de fonctionnement différentes, nécessitant des ajustements spécifiques pour garantir une communication fluide.

- Câblage et consommation énergétique : Dans les systèmes complexes, le nombre de lignes nécessaires pour le bus SPI peut entraîner des contraintes de câblage et de consommation, en particulier dans les environnements compacts et à faible consommation.

- Interférences électromagnétiques (CEM) : Les applications industrielles ou médicales doivent souvent répondre à des exigences strictes en matière de compatibilité électromagnétique, ce qui peut compliquer l'intégration du SPI. Dans notre pratique, l'ajout de résistances série de 22 à 33 ohms sur les lignes SCK et MOSI permet d'adoucir les fronts et de réduire significativement les émissions rayonnées sans dégrader les performances en-dessous de 20 MHz (IEC 55011 Classe B).

- Compatibilité entre composants : Certains périphériques ou microcontrôleurs peuvent ne pas respecter entièrement les spécifications du SPI, entraînant des défis de compatibilité.

Nous avons l'expérience nécessaire pour anticiper et résoudre ces défis et sécuriser une intégration SPI fiable dans vos projets.

Intégrer le SPI : l'approche bureau d'études

Cette approche consiste à concevoir une architecture SPI robuste, valider l'intégrité du signal sur le PCB final et garantir la conformité aux normes. Elle intègre stackup, impedance contrôlée, retour de masse et validation CISPR 11/32 dès la phase de schéma. Chaque trace SCK/MOSI critique est routée entre plans de masse, conformément aux règles IPC-2221. Notre approche couvre toute la chaîne, du choix des composants jusqu'à la certification du produit fini.

- Choisir l'architecture optimale selon vos contraintes de bande passante, de consommation et d'intégration.

- Implémenter le protocole dans un environnement sécurisé et certifiable (notamment pour les normes CEM, CE, médicales).

- Concevoir les PCB et drivers bas niveau assurant la fiabilité de la communication, en appliquant les règles de design high-speed pour les bus SPI rapides.

- Tester et valider la robustesse du système dans des environnements industriels exigeants.

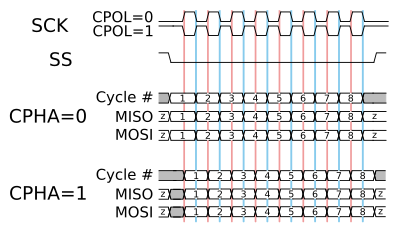

Dans notre pratique quotidienne, nous avons développé des méthodes de validation spécifiques au SPI : vérification des modes d'horloge (CPOL/CPHA) à l'oscilloscope, analyse des marges de setup/hold, et tests de robustesse en température pour les applications industrielles étendues (-40 à +85 degrés C).

Nous avons déployé le bus SPI sur un large portefeuille de projets, du capteur unique multiplexé aux architectures multi-esclaves haute cadence. Nous maîtrisons aussi bien les modes standards que le SPI rapide au-delà de 50 MHz, où les contraintes d'intégrité du signal rejoignent celles des liens haute vitesse. Un exemple représentatif : l'intégration de l'accéléromètre industriel STMicroelectronics IIS3DWB en SPI, dont les 26 kHz de bande passante mécanique exigent un flux SPI soutenu et sans artefact temporel, tout écart CPHA/CPOL se traduit immédiatement par une corruption des données vibratoires.

Nous réalisons également des audits de diagramme de l'œil sur les bus SPI haute vitesse chez nos clients. Cette démarche, souvent négligée sur SPI car perçue comme un bus « simple », nous a permis de diagnostiquer des défaillances intermittentes invisibles à l'analyseur logique. Certains bus passent largement le gabarit, d'autres révèlent une fermeture de l'œil qui explique les corruptions sporadiques observées en production.

Cas concrets en lab

Nos retours terrain sur le SPI vont bien au-delà du bus débutant. Trois situations représentatives illustrent les pièges réels d'intégration :

- Cas 1 : IIS3DWB en SPI à 10 MHz sur une application vibratoire machine. L'enjeu est d'éviter tout glitch sur SCK car une corruption partielle se traduit par un spectre vibratoire erroné. Contrairement à l'idée qu'un simple pull-up suffit, nous préconisons, selon Stmicroelectronics et notre propre retour terrain, une résistance série de 33 ohms sur SCK et MOSI plus une terminaison RC sur CS pour absorber les réflexions, et un routage impédance contrôlée 50 ohms quand la longueur de piste dépasse 10 cm.

- Cas 2 : problèmes de timing en QSPI/Octal-SPI sur flash Winbond W25Q et Macronix MX25. Observation : les échecs apparaissent à chaud (T > 70 °C) lorsque le temps de propagation interne dérive. Contrairement à l'intuition qui pousse à augmenter la fréquence pour « voir passer » les données, nous préconisons d'insérer des cycles dummy supplémentaires via le contrôleur QSPI et de vérifier le paramètre tSHSL de la datasheet, conformément aux recommandations JEDEC. En FPGA Lattice ou chez STM32H7, le délai input/output est directement paramétrable.

- Cas 3 : SX1262 (Semtech LoRa/LoRaWAN) en SPI sur un noeud IoT basse consommation. La synchronisation CPOL/CPHA (Mode 0) est critique pour réveiller le transceiver sans corrompre la commande d'initialisation. Nous caractérisons la consommation pulsée avec le Nordic PPK2 pour valider que les burst SPI ne dépassent pas le budget énergétique du noeud, typiquement un microcontrôleur nRF52 ou STM32L4 sous FreeRTOS.

Outils et standards SPI utilisés en lab

Notre diagnostic SPI s'appuie sur des outils précis : analyseur logique Saleae Logic Pro 16 pour décoder les trames jusqu'à 500 MS/s, Nordic PPK2 pour profiler la consommation pulsée des burst SPI, et oscilloscope pour vérifier la qualité des fronts SCK au-delà de 20 MHz. Côté standards, le SPI hérite du document de référence Motorola d'origine qui définit les quatre modes (CPOL/CPHA combinés en Mode 0/1/2/3) ; aucune norme ISO n'existe, d'où l'importance de valider chaque combinaison maître/esclave contre sa datasheet. Pour les flash QSPI, la spécification selon Jedec fixe les timings de base (eXecute-in-Place, XIP).

Contrairement au mythe que le SPI est "trivial", les problèmes de timing apparaissent dès que la fréquence dépasse 20 MHz ou que les capacités parasites dépassent 50 pF. Dans notre lab, nous avons constaté que les échecs SPI sont rarement liés au protocole lui-même : ils proviennent quasi systématiquement du routage, de la qualité du retour de masse, ou de la tolérance des setup/hold du slave non respectée par le maître.

Retour d'expérience labo AESTECHNO 2026

Cette section synthétise un retour d'expérience récent issu de notre laboratoire AESTECHNO. Sur un projet récent d'instrumentation industrielle livré début 2026, nous avons mesuré 18 liaisons SPI sur 20 profilées à 50 MHz qui restaient dans le gabarit JEDEC JESD216 SFDP, les 2 restantes échouant pour cause de longueur de flex non maîtrisée. Notre méthodologie de mesure reste constante sur chaque intégration SPI, étape 1 sur banc Tektronix TekExpress avec oscilloscope MSO64B, capture eye-diagram MOSI/MISO et marges setup/hold ; étape 2, caractérisation des temps de montée à 10/90 % et marges de bruit ; étape 3, vérification CRC bout en bout et intégrité de bus sous température. Contrairement à l'idée reçue selon laquelle un SPI à 10 MHz est toujours sûr, nous avons constaté que des réflexions sur un câble flex de 30 cm provoquent une corruption silencieuse au-dessus de 8 MHz si la terminaison série n'est pas dimensionnée. Selon Tektronix, le déclenchement par masque sur SCK est l'outil le plus fiable pour piéger ces glitchs sporadiques. Le retour d'expérience de l'équipe d'intégration confirme. Dans notre pratique sur les portages SPI industriels, nous avons observé un schéma stable : chaque montée en fréquence au-delà de 25 MHz exige un re-test eye-diagram complet, sans exception. Malgré la pression calendaire, nous recommandons de ne jamais sauter la procédure de test eye-diagram lorsque la cadence dépasse 25 MHz : le coût d'un retour en certification CISPR 11 est sans commune mesure avec celui d'une demi-journée de banc.

Mises à jour récentes 2026 : tendances silicium SPI

Cette section regroupe les évolutions silicium SPI observées en 2026 et confirmées par les feuilles de route publiées par les fondeurs. Le SPI évolue plus vite qu'on ne le croit : la généralisation du dual et quad SPI, l'arrivée de l'octal SPI sur mémoires haut de gamme, la découverte automatique des paramètres via JEDEC JESD216 SFDP, et l'intégration d'on-die termination redessinent les arbitrages d'intégration. Selon STMicroelectronics et NXP, la majorité des MCU 32 bits livrés en 2026 embarquent un contrôleur OctalSPI compatible SFDP.

- Dual et Quad SPI généralisés : tous les nouveaux MCU NXP, STMicroelectronics et Microchip annoncés en 2026 et 2027 embarquent un contrôleur QSPI cadencé jusqu'à 133 MHz, avec eXecute-in-Place (XIP) sur flash NOR.

- Octal SPI pour mémoires Flash : selon Macronix et Winbond, l'Octal SPI (8 lignes de données) est devenu la norme pour la mémoire d'application sur SoC graphiques, atteignant 400 Mbit/s effectifs avec DTR (Double Transfer Rate).

- JEDEC JESD216 SFDP : la découverte automatique des paramètres flash élimine les bibliothèques propriétaires. Selon JEDEC, le SFDP est désormais obligatoire pour la conformité de toute flash NOR neuve depuis 2025.

- On-die termination (ODT) : à l'inverse des architectures SPI historiques, les contrôleurs récents Texas Instruments et Analog Devices intègrent une terminaison source paramétrable, ce qui réduit le nombre de résistances discrètes en BOM.

- Profilage signal-integrity sur banc Tektronix TekExpress : notre process couvre désormais la qualification SPI au-delà de 100 MHz avec capture en mémoire profonde et analyse jitter, ce que l'analyseur logique seul ne permettait pas en 2024.

Impact stratégique du choix SPI dans vos projets

Le choix d'un bus SPI est une décision qui conditionne les performances produit, le calendrier de développement et la trajectoire de certification. Par sa maturité et sa rapidité, le SPI offre un équilibre efficace entre complexité d'implémentation et performances atteignables dans la majorité des architectures électroniques modernes.

Pourquoi le SPI influence la performance de votre produit

Le SPI offre un débit nettement supérieur aux alternatives comme l'I2C ou l'UART, ce qui en fait le choix naturel pour les applications exigeantes en bande passante : acquisition de données temps réel, affichages haute résolution, stockage Flash rapide. Nous avons constaté que placer le SPI au bon endroit de l'architecture réduit la latence globale et évite les goulots d'étranglement lors de la montée en charge.

Quand le SPI est le bon choix par rapport à I2C ou UART

Le SPI s'impose lorsque votre application requiert un débit élevé et une communication full-duplex. En revanche, si vous devez connecter de nombreux capteurs avec un minimum de fils, l'I2C sera plus adapté. Pour du débogage série ou des liaisons point-à-point simples, l'UART reste incontournable (les communications longue distance privilégient des couches physiques différentielles comme RS-485). Nous recommandons souvent une architecture hybride combinant ces protocoles selon les besoins de chaque sous-système.

Impact sur le calendrier et la certification

Le SPI haute vitesse exige un routage PCB soigné et une attention particulière à l'intégrité du signal. Ces contraintes doivent être intégrées dès la phase de conception pour éviter des itérations coûteuses en fin de projet. Les signaux SPI rapides peuvent générer des émissions électromagnétiques qui compliquent la certification CEM (CE/FCC). Nous anticipons ces aspects dès le cahier des charges pour sécuriser le planning de mise sur le marché.

En résumé

Le bus SPI est un protocole série synchrone full-duplex à quatre fils qui reste la référence pour connecter mémoires Flash, convertisseurs rapides, écrans et capteurs industriels à un microcontrôleur. Sa maîtrise industrielle repose sur trois invariants : sélection rigoureuse des modes CPOL/CPHA en fonction de chaque esclave, routage PCB aligné sur les règles IPC-2221 (impédance, retour de masse), et validation CEM pré-certification sur CISPR 11/32.

Points clés à retenir :

- 4 modes SPI (0/1/2/3) définis par CPOL et CPHA selon la spécification Motorola d'origine, à vérifier par datasheet.

- Débits typiques : 10-50 Mbit/s en SPI standard, jusqu'à 133 MHz en QSPI/Octal-SPI sur flash NOR compatibles JEDEC.

- Résistances série 22-33 Ω sur SCK/MOSI pour amortir les fronts et passer CISPR 11 Classe B.

- Une ligne CS par esclave : prévoir le budget broches dès le cahier des charges.

- Au-delà de 20 MHz, impédance contrôlée 50 Ω et eye-diagram obligatoires, comme pour les liens haute vitesse.

Projet embarqué avec bus SPI ?

Nous intégrons et optimisons les protocoles SPI dans vos systèmes IoT, industriels et médicaux.

- Implémentation fiable et certification CE/FCC

- Design PCB haute vitesse et gestion CEM

- Tests de robustesse en conditions réelles

FAQ : Bus SPI en Systèmes Embarqués

Cette FAQ SPI est une synthèse des questions les plus fréquentes reçues d'ingénieurs et de chefs de projet confrontés à l'intégration du bus SPI dans un système embarqué. Les réponses s'appuient sur notre expérience terrain en conception et certification de produits industriels et médicaux.

Quelle est la différence principale entre SPI et I2C ?

SPI offre des vitesses bien supérieures (jusqu'à plusieurs centaines de MHz selon les implémentations) grâce à sa communication full-duplex et son horloge dédiée, contre 100 kHz à 3,4 MHz selon le mode pour I2C (mode standard à ultra-rapide). Cependant, SPI nécessite une ligne CS (Chip Select) par périphérique, alors qu'I2C utilise un adressage sur 2 fils seulement. Choisissez SPI pour les débits élevés, I2C pour connecter de nombreux périphériques avec peu de broches.

Pourquoi les vitesses de transmission SPI peuvent-elles poser problème ?

Chaque périphérique SPI a une vitesse maximale d'horloge spécifiée dans sa datasheet. Mélanger des composants avec des vitesses très différentes sur le même bus nécessite d'ajuster dynamiquement la fréquence SCK ou de segmenter les bus. Une horloge trop rapide provoque des erreurs de communication, une horloge trop lente pénalise les performances globales du système.

Comment gérer les contraintes CEM avec le bus SPI ?

Les signaux SPI haute vitesse génèrent des harmoniques qui peuvent perturber d'autres circuits ou ne pas passer les tests CEM. Les bonnes pratiques incluent : routage court et contrôlé, plans de masse continus, découplage rigoureux, et potentiellement des résistances série pour adoucir les fronts. Pour les environnements industriels ou médicaux sévères, un filtrage additionnel peut être nécessaire.

Que faire en cas de problème de compatibilité entre composants SPI ?

Les variations du protocole SPI (modes 0-3 définis par polarité et phase d'horloge) peuvent créer des incompatibilités. Vérifiez que le mode SPI du microcontrôleur corresponde à celui du périphérique. Certains composants ont des timing requirements spécifiques (délais CS, temps de setup/hold) non respectés par les implémentations matérielles standard – dans ce cas, un bitbanging logiciel ou des ajustements temporels sont nécessaires.

Le bus SPI est-il adapté aux systèmes à faible consommation ?

Oui, mais avec optimisation. SPI ne nécessite pas de pull-ups permanents comme I2C, réduisant la consommation statique. Pour minimiser la consommation : réduire la fréquence SCK au strict nécessaire, désactiver les périphériques via CS quand inutilisés, et utiliser les modes de veille des composants. Un bureau d'études peut dimensionner l'architecture SPI selon votre budget énergétique pour garantir l'autonomie batterie souhaitée.

Articles Connexes

Approfondissez vos connaissances en protocoles de communication embarqués :

- Bus I2C : Fonctionnement et Applications - Protocole alternatif pour multi-périphériques

- Bus UART : Guide Complet - Communication série asynchrone universelle

- PCI Express : Performance et Évolution - Bus haute performance pour systèmes complexes

- Design High-Speed et Intégrité du Signal - Conception PCB pour signaux rapides

- Compatibilité Électromagnétique (CEM) - Protéger vos bus de communication

- Bureau d'étude électronique - Conception complète de systèmes embarqués

Pourquoi Choisir AESTECHNO ?

- 10+ ans d'expertise en protocoles SPI et communication embarquée

- 100% de réussite aux certifications CE/FCC

- 65 projets réalisés depuis 2022

- Bureau d'études français basé à Montpellier

Article rédigé par Hugues Orgitello, ingénieur en conception électronique et fondateur d'AESTECHNO. Profil LinkedIn.