La conception de produit à base de mémoire DDR est devenu une routine chez AESTECHNO. Développer des produits avec de la mémoire vive rapide devient aujourd’hui essentiel.

Cela permet par exemple une qualité d’affichage vidéo efficace et performante. Nous prenons aujourd’hui tous pour acquis nos téléphones portables. Cependant cela nécessite des millions de recherche et développement. Ces produits ultra performants donnent un sentiment de sous qualité très vite aux produits mal conçus.

Il est donc désormais indispensable d’avoir des produits rapides et bien conçus pour nos clients !

Le routage de la LPDDR4 peut sembler mystérieux et complexe, mais il n’en n’est rien. La LPDDR4 est une variante de la DDR4 qui est la 4ième version de la RAM DDR.

La DDR-RAM pour double data rate Random Access Memory, mémoire à accès aléatoire à double débit. Pour faire simple c’est de la mémoire vive qui communique les données à deux fois la vitesse de l’horloge.

La LPDDR est une variante dite low power. Elle permet de réduire la consommation. En pratique, selon les configurations, la différence peut être minime.

Router de la mémoire, ce n’est pas simplement relier les fils. C’est aussi comprendre les phénomènes physiques associés. Le signal ne se déplace pas à la vitesse de la lumière, mais à un facteur de celui-ci. La variable ayant le plus d’effet est la constante diélectrique. La vitesse de déplacement du signal aura un impact sur le skew. Il faut aussi maitriser le concept d’impédance globale et d’impédance locale. Les changements d’impédances sont à proscrire.

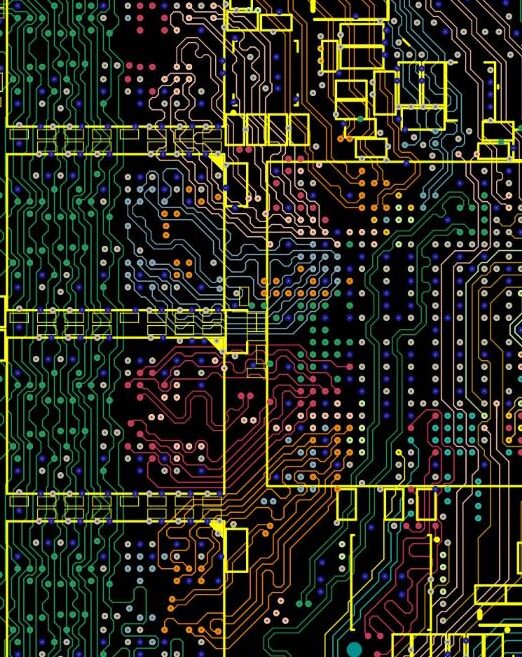

Donc choisir son matériau et son épaisseur est critique. La construction d’un PCB se fait via l’édition d’un Master drawing. Ce document permet de donner toutes les informations de construction d’un PCB. Industrialiser un PCB, c’est s’assurer de sa fabricabilité dans un environnement industriel. C’est réduire le nombre d’échec de fabrication d’une usine tout en gardant les performances plus proches de l’objectif. C’est un compromis entre sous et sur qualité.

La construction du PCB et de son stack-up démarre au moment où on commence le schéma, et fini vraiment lorsque le routage est terminé. C’est un processus de création qui tend vers une solution finale. Le compromis entre performances et cout de fabrication.

Si choisir un stack-up peut sembler inutile pour 75% des produits, et prendre celui par défaut peut suffire, sur un produit avec de la DDR4 ou de la LPDDR4 n’est pas une option.

Si certains stubs sont encore possibles en DDR4 et LPDDR4, à l’avenir en DDR5 et LPDDR5 ce ne sera plus possible de les ignorer. Donc autant commencer à s’en préoccuper. Une stratégie de routage dès le démarrage est indispensable.

Signaux DDR:

La DDR est routée en groupes. Si vous avez une mémoire x4, vous avez 4 signaux DQ à router avec sa paire différentielle DQS. Une mémoire x8, 8 signaux DQ[0-7] et sa paire DQS. Et je vous laisse deviner pour la mémoire en x16. Dans l’idéal, il peut être plus simple à router en x4 ou x8. Router en x16 est plus complexe. Il est préférable de router ces pistes sur la même couche pour des aspects de skew et d’industrialisation.

Les groupes sont donc des groupes de DQ, exemple DQ groupe 0 à 3 pour une mémoire vive en 32 bits avec 4 groupes de 8 DQ.

Les autres groupes sont les groupes de « command & address ». Ils peuvent différer en fonction des technologies de RAM LPDDR ou DDR par exemple, et en fonction de la typologie interne de la mémoire vive. Ces groupes vont à mi vitesse des groupes DQ.

Il est important de créer ses groupes dans votre outil de conception PCB pour bien résoudre les différents problèmes de skew. Le skew est fondamentalement une différence de temps d’arrivé entre deux signaux. Un signal qui arrive en retard ou en avance ne va pas respecter les délais acceptables pour la mémoire. (Le temps de setup ou temps de hold). Donc il faut que les signaux arrivent au boitier de ram au même moment car c’est un bus parallèle. Les valeurs sont généralement données par les fabricants. Il est préférable de les recalculer systématiquement.

Pour simplifier le routage, les DQS sont des signaux de strobe pour permettre d’avoir une longueur un peu différente entre les groupes. Donc, les groupes permettent d’avoir un jeu de longueur. Ce qui est plus simple que de router tous les signaux à la même longueur car ils sont nombreux.

La longueur maximum dépend plus du matériau de PCB et de sa construction, et pas vraiment des recommandations du fabricant en pratique. Être légèrement plus long n’est pas si dramatique avec un bon matériau et bon routage. Je recommande de placer la mémoire d’ailleurs plutôt éloignée quand on ne maitrise pas trop le routage DDR pour se simplifier la vie lors de l’ajustement des longueurs.

Respecter l’impédance tout le long, permet de minimiser les réflexions. En gros une réflexion c’est un peu comme de l’écho. Quand vous criez dans un tunnel, il y a de l’écho qui vous revient. Si le but étant de maximiser le son qui arrive au récepteur, c’est toute cette énergie qui est perdue. Pire elle peut être néfaste à l’émetteur si le signal est trop fort. L’impédance est une conséquence de la construction géométrique et du choix des matériaux. Sachant qu’au début d’une piste et à la fin d’une piste le matériau est toujours le même. En définitive votre travail est purement un exercice de géométrie ! C’est un retour en classe de mathématique. L’impédance locale est importante. La largeur de la piste nominale est calculée par votre outil. C’est aucun problème pour un bon outil de CAO. Notez qu’il faut bien se renseigner sur l’algorithme derrière le calcul et ses limites. L’impédance locale c’est lorsque votre piste à impédance contrôlé se retrouve à proximité d’une autre piste ou d’un connecteur, d’un via, d’un plan de référence, ou tout être élément non pris en compte dans le calcul d’impédance. Un via à la masse de référence à proximité d’une piste va influer significativement l’impédance et ajouter de la réflexion.

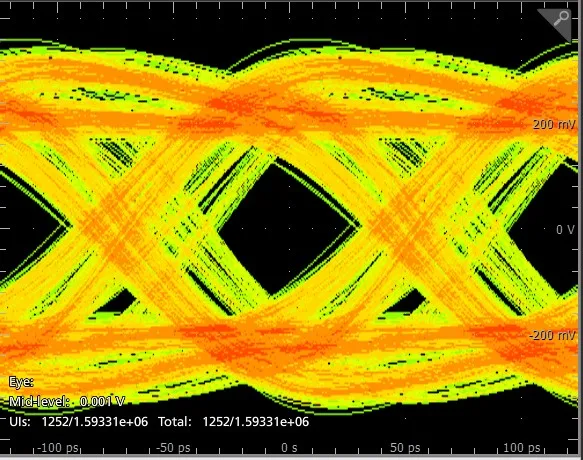

Dans un monde idéal, je vous recommande d’avoir un paramètre S11 inférieur ou égal à -15dB aux fréquences désirées. Le S11 est le critère numéro 1 pour vous donner la qualité votre routage en impédance constante. C’est le taux de réflexion de votre piste dans votre système. Il peut être obtenu par une extraction parasitique via un outil de simulation, ou une mesure via un VNA.

Utiliser un matériau bon marché cela se paye. Il vaut mieux faire des simulations. Les simulations coutent cher et sont difficiles. Les outils permettant ce type de simulations sont très complexes. Si vous ne n’êtes pas un expert, il est préférable de faire à quelqu’un qui déjà habitué à ces outils.

Les matériaux plus chers permettent de garantir une certaine sécurité industrielle. Il sera plus facile de garantir les performances. Le problème est que parfois il n’est pas acceptable de payer plus cher. Accepteriez-vous de payer un téléphone 5 000€ ? Il est préférable d’utiliser ces outils pour réduire le cout des matériaux.

Je rappelle que les normes IPC sont des normes qui n’ont rien d’obligatoire. Elles sont là pour simplifier et se mettre d’accord sur un outil industriel. Dans certains cas, l’industrie est en avance sur les IPC. Il faut en être conscient car 100% IPC n’est pas possible à mon sens. En fonction des situations, l’IPC n’est pas une bonne solution ou la meilleure solution. Parfois l’IPC ne définit pas de solution. La définition du métier d’ingénieur est de savoir faire des compromis.

Dans le routage DDR connaitre les IPC est essentiel. Mais souvent comme dans tout routage complexe, il est nécessaire de s’en affranchir.

Il peut être tentant de lire des articles sur le routage DDR comme celui ci. Je vous conseille fortement de rester critique. Bon nombre de ces articles sur internet proposent effectivement des exemples de solution. Cependant quand vous aurez une expérience plus poussée, vous vous rendrez vite compte que bien que le routage puisse sembler joli, il est au final assez mauvais. La plupart du temps ces routages ne respectent pas les groupes. Oublier cela c’est faire un projet uniquement pour faire du prototype. En production ce type de routage ne tient pas très longtemps.

Pourquoi Choisir AESTECHNO ?

- 10+ ans d’expertise en routage DDR/LPDDR haute vitesse

- 100% de réussite aux qualifications mémoire

- 50+ projets avec interfaces DDR4/DDR5 livrés

- Bureau d’études français basé à Montpellier

Projet avec LPDDR4/DDR5 ? Expertise AESTECHNO

Le routage mémoire haute vitesse est notre spécialité. Nos experts vous accompagnent :

- Stack-up PCB optimisé pour DDR/LPDDR

- Simulation intégrité signal et eye diagrams

- Routage groupes DQ/DQS conforme aux design rules

- Validation S11 et qualification industrielle

AESTECHNO peut développer vos produits avec de la DDR.

Pour aller plus loin dans la compréhension des interfaces mémoire, nous vous recommandons notre comparatif DDR4 vs DDR5 qui détaille les évolutions entre générations. Les modules NVIDIA Jetson utilisent notamment de la LPDDR4x, ce qui en fait un excellent exemple d’intégration mémoire haute performance en embarqué. Les contraintes de routage LPDDR4 rejoignent les problématiques plus larges du design high-speed, et s’inscrivent dans notre méthodologie globale de conception de produits électroniques.

LPDDR4 : un choix stratégique pour vos produits embarqués

Le choix de la technologie mémoire est une décision stratégique qui impacte directement la compétitivité de vos produits. Chez AESTECHNO, nous accompagnons régulièrement des directeurs techniques et des décideurs dans cette réflexion, car la mémoire influence trois axes fondamentaux : la performance perçue par l’utilisateur, l’autonomie sur batterie et le comportement thermique du produit.

Performance et expérience utilisateur

La LPDDR4 offre une bande passante suffisante pour la majorité des applications embarquées actuelles : affichage vidéo fluide, traitement d’images, interfaces utilisateur réactives. Pour un produit destiné au marché grand public ou industriel, une mémoire sous-dimensionnée se traduit immédiatement par une perception de lenteur qui nuit à l’image de marque.

Autonomie et contraintes thermiques

La variante Low Power de la DDR4 réduit la consommation par rapport à la DDR4 standard. Dans un produit sur batterie — smartphone, tablette industrielle, terminal portable — ce gain est un avantage concurrentiel direct. De plus, une consommation réduite signifie moins de dissipation thermique, ce qui simplifie la conception mécanique et réduit les risques de throttling en environnement contraint.

LPDDR4, DDR4 ou DDR5 : quel choix pour votre projet ?

Nous avons constaté que le choix entre ces technologies dépend principalement du contexte produit :

- LPDDR4/LPDDR4x : produits sur batterie, embarqué compact, contraintes thermiques fortes. C’est le choix naturel pour les SoC ARM (type NVIDIA Jetson, NXP i.MX8).

- DDR4 : applications industrielles fixes, systèmes sans contrainte d’autonomie, budgets serrés. Excellente maturité industrielle et chaîne d’approvisionnement stable.

- DDR5 : projets nécessitant une bande passante élevée (IA, traitement vidéo multi-flux) ou une durée de vie produit longue. Consultez notre guide DDR4 vs DDR5 pour approfondir cette comparaison.

Impact sur la longévité produit

La LPDDR4 bénéficie aujourd’hui d’une maturité industrielle solide, avec de nombreux fabricants et une disponibilité stable. Pour un produit dont la durée de vie dépasse 5 à 7 ans, nous recommandons de vérifier les roadmaps de fin de vie des composants mémoire dès la phase de conception. Un choix mémoire mal anticipé peut entraîner un redesign coûteux en milieu de cycle de vie.

FAQ : LPDDR4 et Routage Mémoire Haute Vitesse

Qu’est-ce que le paramètre S11 et pourquoi viser -15 dB ?

Le S11 mesure le taux de réflexion du signal sur une piste (coefficient de réflexion). Un S11 de -15 dB signifie que seulement 5,6% de l’énergie est réfléchie, 94,4% est transmise – excellent pour l’intégrité du signal. S11 > -10 dB indique des problèmes d’impédance (réflexions importantes). Le S11 s’obtient par simulation électromagnétique (extraction parasitique) ou mesure avec un analyseur de réseau vectoriel (VNA). Pour LPDDR4/DDR4, un bon S11 garantit des eye diagrams conformes.

Pourquoi les simulations électromagnétiques sont-elles si coûteuses pour les interfaces DDR ?

Les outils de simulation EM (HFSS, CST, HyperLynx) nécessitent : licences coûteuses (15 000-50 000 €/an), expertise technique pointue (formation 6-12 mois), temps de calcul important (heures/jours pour modèles 3D complexes). Mais elles permettent d’utiliser des matériaux PCB économiques en compensant par un design optimisé. Alternative : matériaux premium (Rogers, Isola) qui tolèrent mieux les imperfections mais coûtent 3-5x plus cher que le FR-4 standard.

Que signifie « respecter les groupes » en routage DDR ?

En DDR, les signaux sont organisés en groupes (byte lanes) : 8 bits de données DQ + 1 paire de strobe DQS + masque DM. Tous les signaux d’un même groupe doivent avoir des longueurs égalisées (±25 mils) et arriver simultanément pour respecter les fenêtres de setup/hold. Ne pas respecter les groupes fonctionne en prototype (contraintes timing relâchées) mais échoue en production industrielle (variations process, températures, vieillissement). C’est la différence entre « ça marche » et « certifiable ».

Les normes IPC sont-elles suffisantes pour routage DDR complexe ?

Les normes IPC fournissent une base essentielle (largeurs de pistes, espacements, empilements standards) mais ne couvrent pas tous les cas avancés : routages DDR très haute vitesse (>3200 MT/s), contraintes spécifiques fabricants (variations process), optimisations pour matériaux non-standard. Sur projets complexes, il faut parfois déroger aux IPC avec justification technique (simulations, mesures). Le métier d’ingénieur consiste à faire des compromis éclairés entre normes, coûts et performance.

Pourquoi tant d’exemples de routage DDR sur Internet sont-ils mauvais ?

Beaucoup de tutoriels montrent des routages visuellement corrects mais techniquement défaillants : groupes non respectés, longueurs mal égalisées, références de plan discontinues, stubs excessifs. Ces routages peuvent fonctionner sur des prototypes en conditions idéales (température stable, composants triés) mais échouent en production (variations ±40°C, composants worst-case, vieillissement). Pour du matériel certifiable industriel, il faut suivre les design guides des fabricants de SoC/mémoire et valider par eye diagrams.

Articles Connexes

- ⚡ Design High-Speed et Intégrité du Signal – Méthodologie pour routages critiques

- 💾 DDR4 vs DDR5 – Évolutions et contraintes de conception

- 🖥️ Processeurs Jetson NVIDIA – LPDDR4x pour IA embarquée

- 📐 Conception Produits Électroniques – Méthodologie de conception

- 📐 Conception de PCB – Stack-up et matériaux